ZHCSV24 March 2024 LMK05318B-Q1

PRODUCTION DATA

- 1

- 1 特性

- 2 應用

- 3 說明

- 4 引腳配置和功能

- 5 規格

- 6 參數測量信息

-

7 詳細說明

- 7.1 概述

- 7.2 功能方框圖

- 7.3

特性說明

- 7.3.1 振蕩器輸入 (XO_P/N)

- 7.3.2 基準輸入(PRIREF_P/N 和 SECREF_P/N)

- 7.3.3 時鐘輸入連接和端接

- 7.3.4 基準輸入多路復用器選擇

- 7.3.5 無中斷切換

- 7.3.6 基準輸入上的間隙時鐘支持

- 7.3.7 輸入時鐘和 PLL 監控、狀態和中斷

- 7.3.8

PLL 關系

- 7.3.8.1 PLL 頻率關系

- 7.3.8.2 模擬 PLL(APLL1、APLL2)

- 7.3.8.3 APLL 參考路徑

- 7.3.8.4 APLL 相位頻率檢測器 (PFD) 和電荷泵

- 7.3.8.5 APLL 反饋分頻器路徑

- 7.3.8.6 APLL 環路濾波器(LF1、LF2)

- 7.3.8.7 APLL 壓控振蕩器(VCO1、VCO2)

- 7.3.8.8 APLL VCO 時鐘分配路徑(P1、P2)

- 7.3.8.9 DPLL 基準 (R) 分頻器路徑

- 7.3.8.10 DPLL 時間數字轉換器 (TDC)

- 7.3.8.11 DPLL 環路濾波器 (DLF)

- 7.3.8.12 DPLL 反饋 (FB) 分頻器路徑

- 7.3.9 輸出時鐘分配

- 7.3.10 輸出通道多路復用器

- 7.3.11 輸出分頻器 (OD)

- 7.3.12 時鐘輸出 (OUTx_P/N)

- 7.3.13 無毛刺輸出時鐘啟動

- 7.3.14 時鐘輸出連接和端接

- 7.3.15 輸出同步 (SYNC)

- 7.4 器件功能模式

- 7.5 編程

- 8 應用和實施

- 9 器件和文檔支持

- 10修訂歷史記錄

- 11機械、封裝和可訂購信息

5.8 典型特性

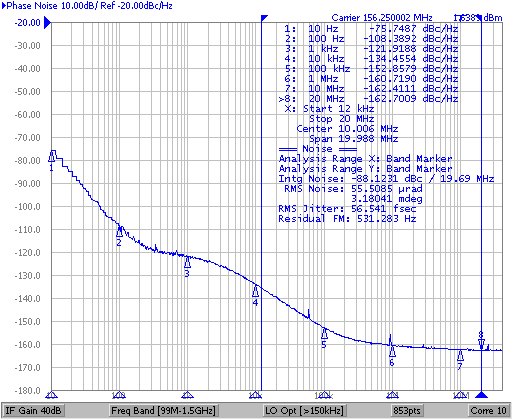

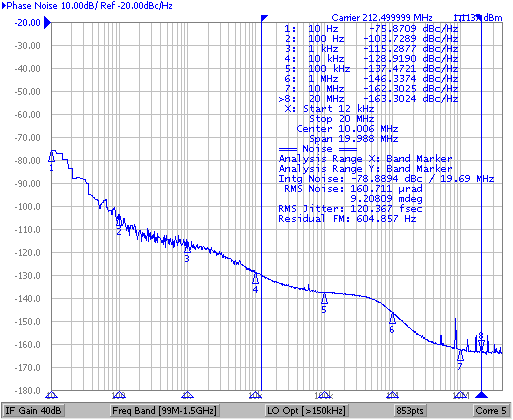

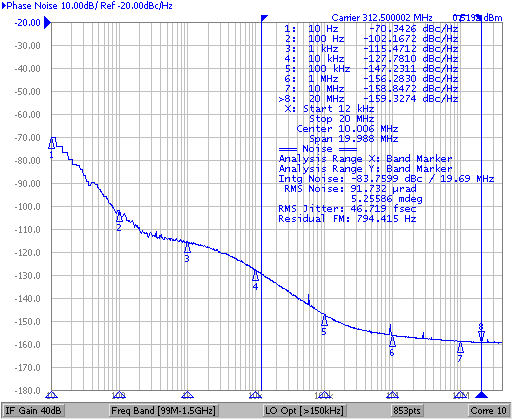

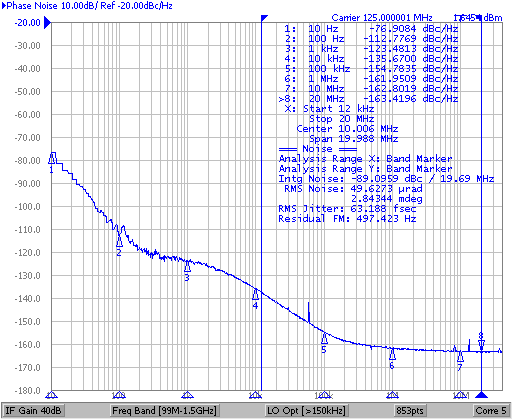

除非另有說明:VDD = 3.3V,VDDO = 1.8V,TA = 25°C,測量 AC-LVPECL 輸出。DPLL:fREF = 25MHz,fTDC = 25MHz,BWDPLL = 10Hz,DPLL 鎖定至基準。APLL1:fXO = 48MHz,fPD1 = 24MHz (fXO÷2),fVCO1 = 2500MHz,BWAPLL1 = 2.5kHz,DPLL 模式。APLL2:fPD2 = 138.8MHz (fVCO1÷18),BWAPLL2 = 500kHz,圖 5-10和圖 5-11 的級聯 APLL2 模式。不同頻率偏移下的 PLL 輸出時鐘相位噪聲取決于不同的噪聲源,例如外部時鐘輸入源(REF IN、XO)和內部噪聲源(PLL、VCO)以及配置的 PLL 環路帶寬(BWREF-DPLL、BWTCXO-DPLL、BWAPLL)。每個外部時鐘源 (fSOURCE) 所示的相位噪聲曲線都歸一化為 PLL 輸出頻率 (fOUT),具體方法是將 20×LOG10(fOUT / fSOURCE) 添加到測得的源相位噪聲。

| 抖動 = 40fs RMS(12kHz 至 20MHz) |

| DPLL 模式(禁用 APLL2) |

| 抖動 = 56fs RMS(12kHz 至 20MHz) |

| DPLL 模式(禁用 APLL2) |

| 抖動 = 74fs RMS(12kHz 至 20MHz) |

| DPLL 模式(禁用 APLL2) |

| 抖動 = 120fs RMS(12kHz 至 20MHz) |

| 具有級聯 APLL2 的 DPLL 模式 |

| fVCO2 = 5737.5MHz |

| 注入電源的 25mVpp 噪聲(VDD = 3.3V,VDDO = 1.8V) |

| DJSPUR (ps pk-pk) = 2 × 10(dBc/20) / (π × fOUT) × 1E6,其中 dBc 是 PSNR 雜散電平(以 dBc 為單位),fout 是輸出頻率(以 MHz 為單位) |

| 抖動 = 47fs RMS(12kHz 至 20MHz) |

| DPLL 模式(禁用 APLL2) |

| 抖動 = 63fs RMS(12kHz 至 20MHz) |

| DPLL 模式(禁用 APLL2) |

| 抖動 = 117fs RMS(12kHz 至 20MHz) |

| 具有級聯 APLL2 的 DPLL 模式 |

| fVCO2 = 5598.72MHz |

| 注入電源的 50mVpp 噪聲(VDD = 3.3V,VDDO = 3.3V) |