ZHCSUV2A April 2024 – October 2024 UCC27614-Q1

PRODUCTION DATA

- 1

- 1 特性

- 2 應(yīng)用

- 3 說明

- 4 引腳配置和功能

- 5 規(guī)格

- 6 詳細(xì)說明

- 7 應(yīng)用和實施

- 8 電源相關(guān)建議

- 9 布局

- 10器件和文檔支持

- 11修訂歷史記錄

- 12機(jī)械、封裝和可訂購信息

封裝選項

請參考 PDF 數(shù)據(jù)表獲取器件具體的封裝圖。

機(jī)械數(shù)據(jù) (封裝 | 引腳)

- D|8

- DGN|8

- DSG|8

散熱焊盤機(jī)械數(shù)據(jù) (封裝 | 引腳)

訂購信息

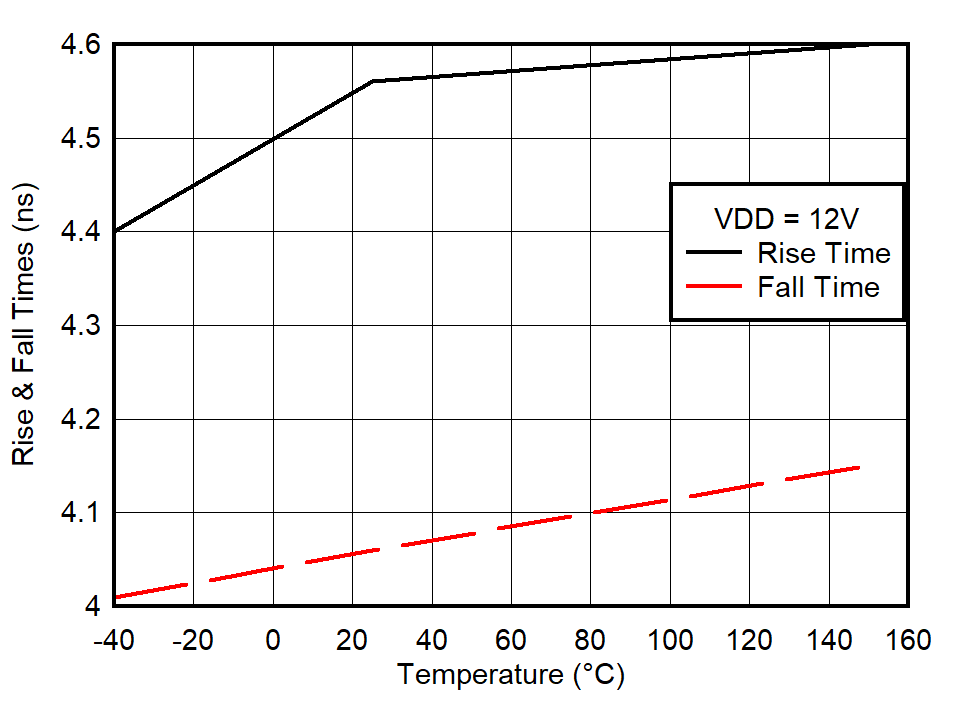

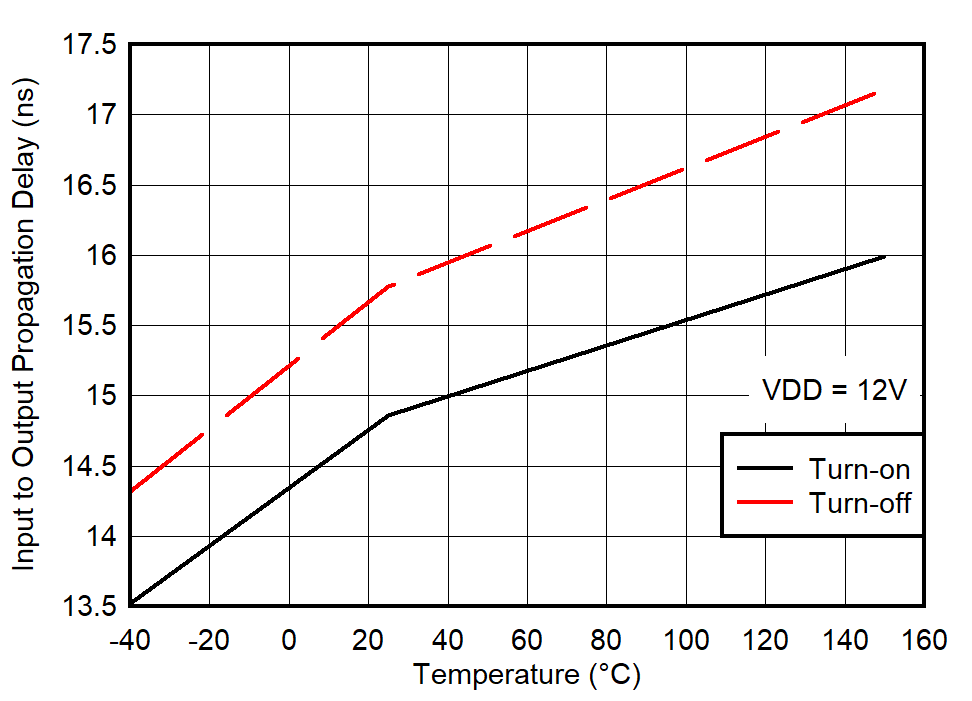

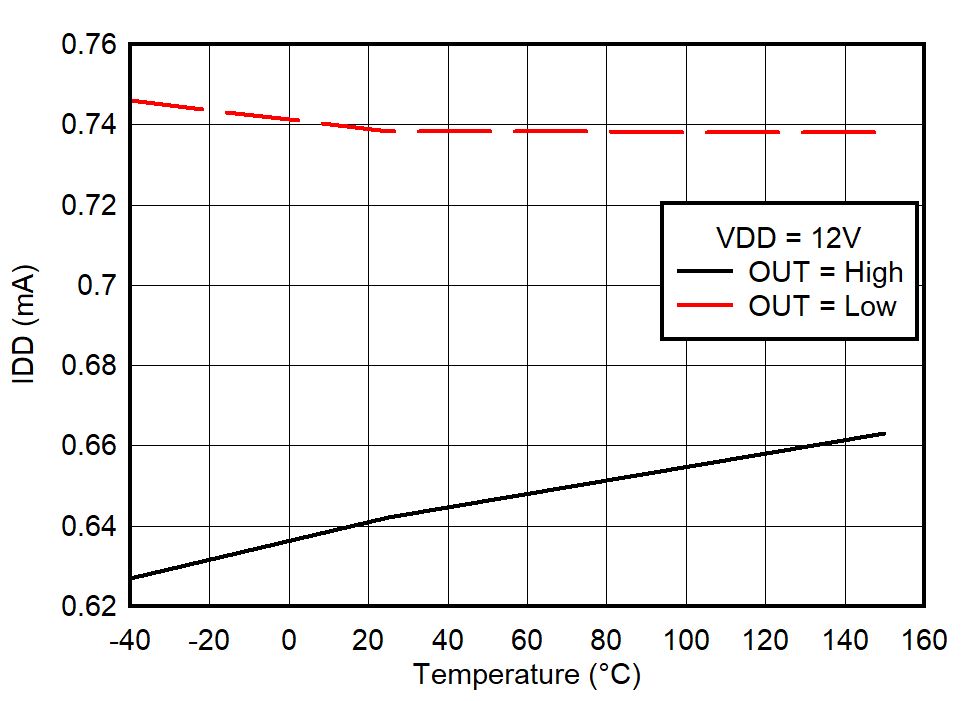

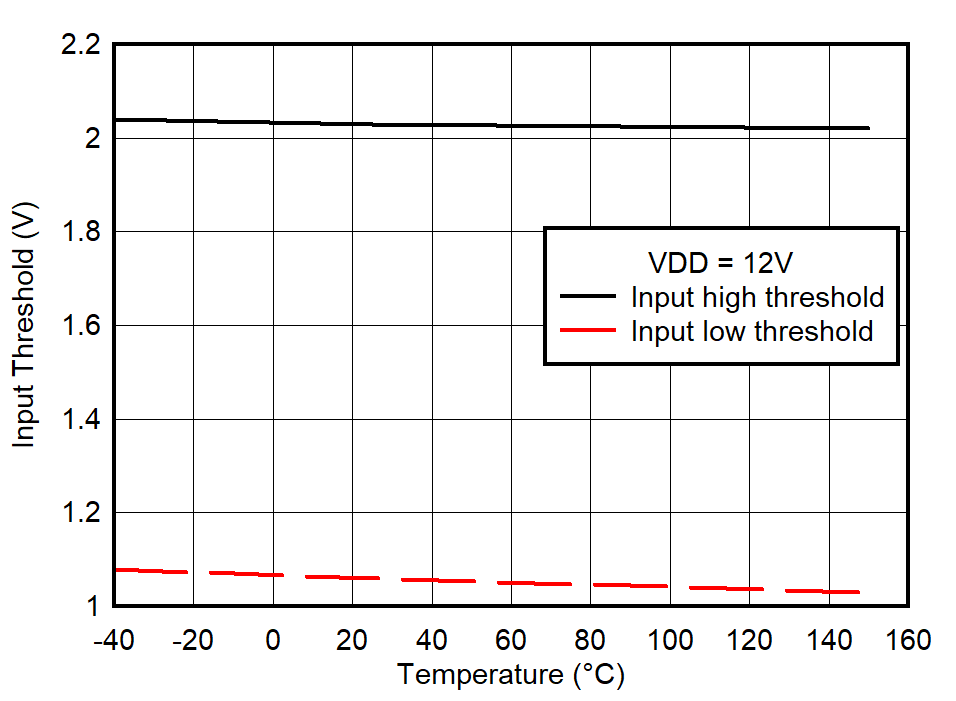

5.8 典型特性

除非另有說明,否則 VDD = 12V、IN+ = 3.3V、IN- = GND、TJ = 25°C 且空載

圖 5-4 峰值拉電流與 VDD 間的關(guān)系

圖 5-4 峰值拉電流與 VDD 間的關(guān)系

| CLOAD = 1.8nF |

| CLOAD = 1.8nF |

| CLOAD = 1.8nF |

圖 5-12 工作電源電流與 VDD 間的關(guān)系

圖 5-12 工作電源電流與 VDD 間的關(guān)系 圖 5-14 輸入閾值與 VDD 間的關(guān)系

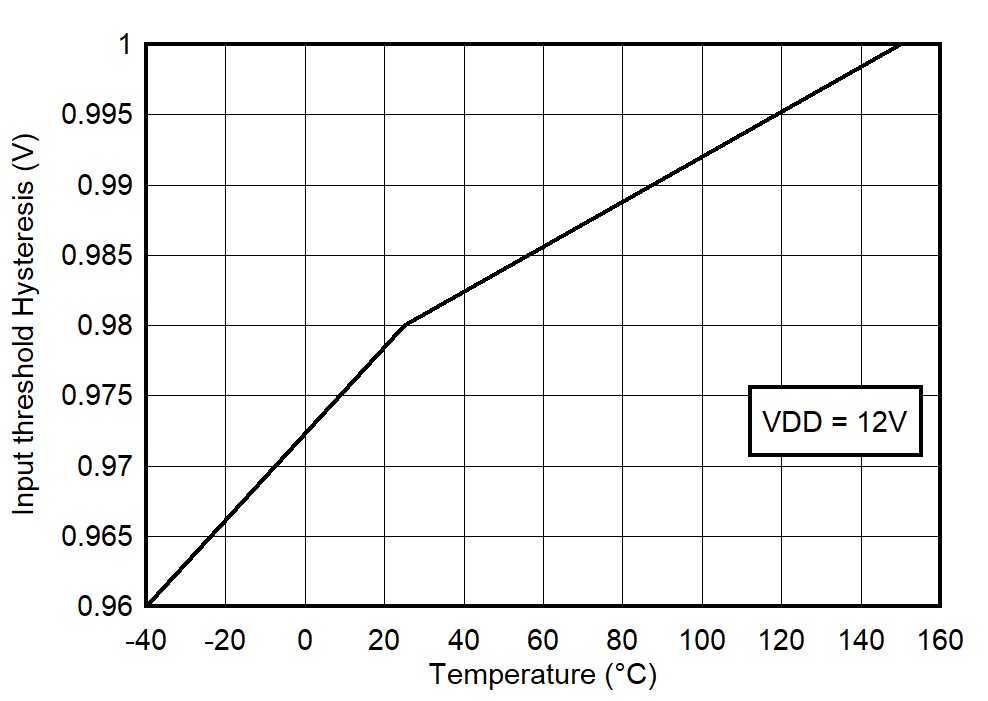

圖 5-14 輸入閾值與 VDD 間的關(guān)系 圖 5-16 輸入閾值遲滯與溫度間的關(guān)系

圖 5-16 輸入閾值遲滯與溫度間的關(guān)系 圖 5-18 輸出上拉電阻與溫度間的關(guān)系

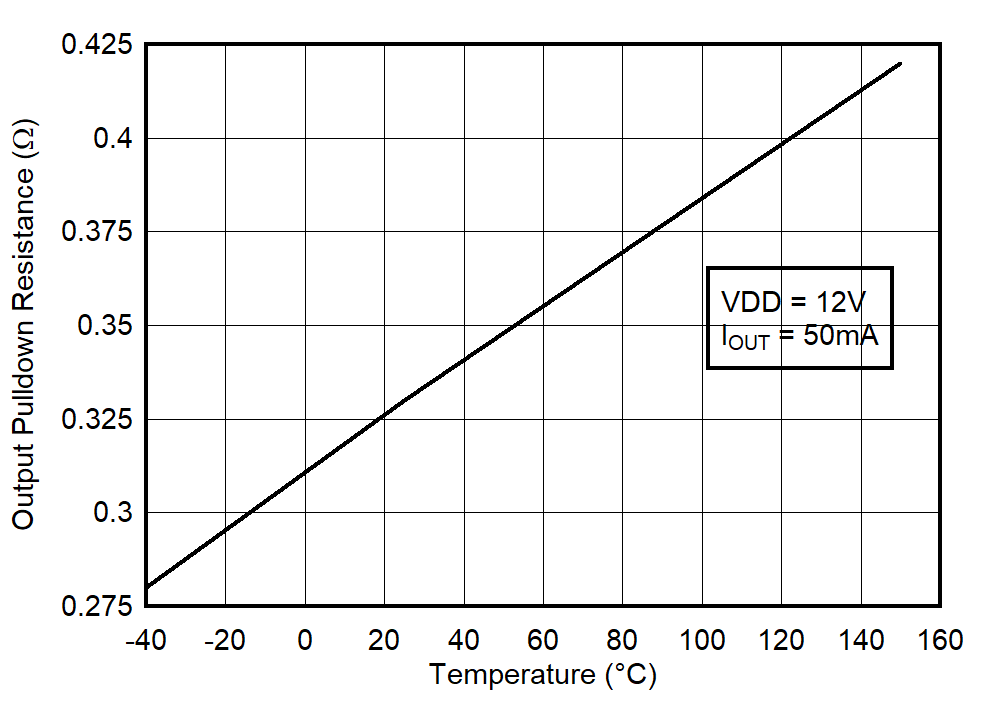

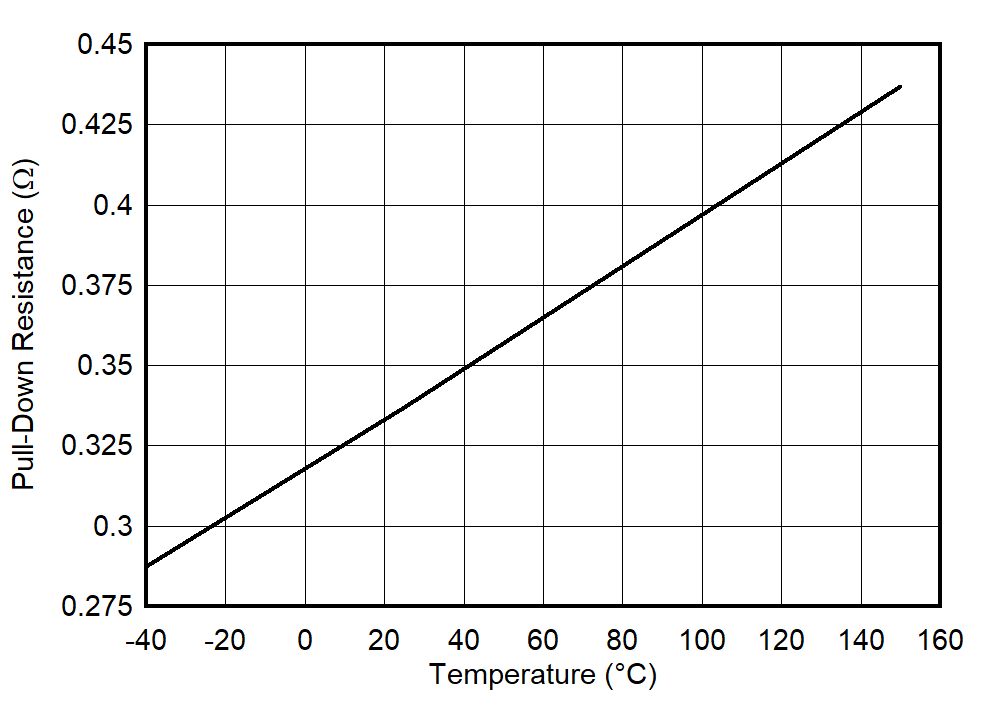

圖 5-18 輸出上拉電阻與溫度間的關(guān)系 圖 5-20 輸出下拉電阻與溫度間的關(guān)系

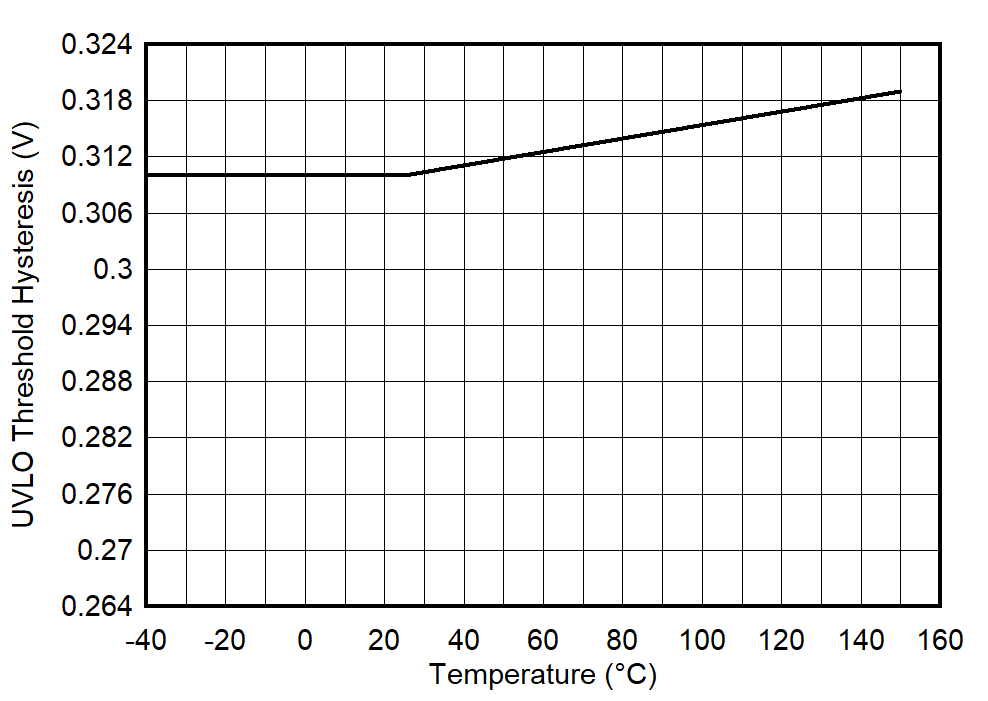

圖 5-20 輸出下拉電阻與溫度間的關(guān)系 圖 5-22 UVLO 遲滯與溫度間的關(guān)系

圖 5-22 UVLO 遲滯與溫度間的關(guān)系 圖 5-5 峰值灌電流與 VDD 間的關(guān)系

圖 5-5 峰值灌電流與 VDD 間的關(guān)系

| CLOAD = 1.8nF |

| CLOAD = 1.8nF |

| CLOAD = 1.8nF |

圖 5-13 工作靜態(tài)電源電流與溫度間的關(guān)系

圖 5-13 工作靜態(tài)電源電流與溫度間的關(guān)系 圖 5-15 輸入閾值與溫度間的關(guān)系

圖 5-15 輸入閾值與溫度間的關(guān)系 圖 5-17 輸出上拉電阻與 VDD 間的關(guān)系

圖 5-17 輸出上拉電阻與 VDD 間的關(guān)系 圖 5-19 輸出下拉電阻與 VDD 間的關(guān)系

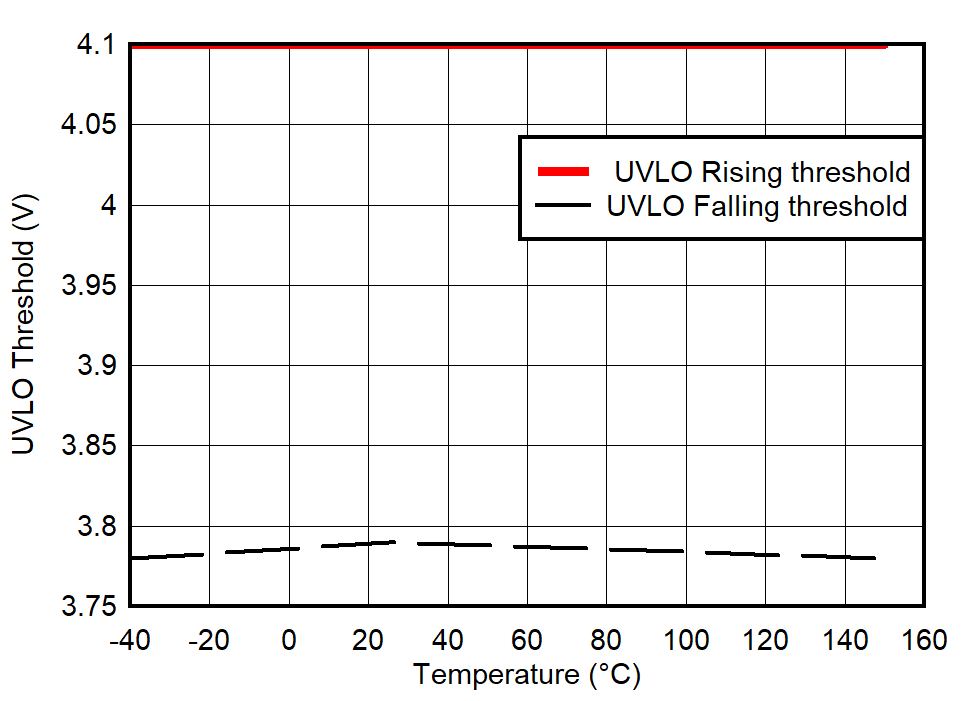

圖 5-19 輸出下拉電阻與 VDD 間的關(guān)系 圖 5-21 UVLO 閾值與溫度間的關(guān)系

圖 5-21 UVLO 閾值與溫度間的關(guān)系