ZHCAFS1A February 2019 – September 2025 LM1117-Q1 , LM317 , LP2951 , LP2951-Q1 , LP2985 , TL1963A , TL1963A-Q1 , TLV1117 , TLV709 , TLV755P , TLV761 , TLV766-Q1 , TLV767 , TLV767-Q1 , TPS709 , TPS709-Q1 , TPS715 , TPS745 , TPS7A16A , TPS7A16A-Q1 , TPS7A25 , TPS7A26 , TPS7A43 , TPS7A44 , TPS7A47 , TPS7A47-Q1 , TPS7A49 , TPS7B63-Q1 , TPS7B68-Q1 , TPS7B69-Q1 , TPS7B81 , TPS7B81-Q1 , TPS7B82-Q1 , TPS7B83-Q1 , TPS7B84-Q1 , TPS7B85-Q1 , TPS7B86-Q1 , TPS7B87-Q1 , TPS7B88-Q1 , TPS7B91 , TPS7B92 , TPS7C84-Q1 , UA78L , UA78M , UA78M-Q1

1 簡介

LDO 具有相對簡單性和成本優勢,因此是電子電源設計中最常見的 DC/DC 轉換器。隨著應用日益集成化與小型化,電源設計需向更小尺寸、更低成本方向發展,這導致 LDO 的使用量不斷增加。由于 LDO 屬于線性轉換器,本身存在功耗,因此熱性能成為系統設計中愈發重要的考量因素。盡管 JEDEC 已制定了半導體熱性能參數的統一測量與報告標準,但該標準在熱性能優化方面尚未完善。影響熱性能的最重要因素之一在于系統設計人員,即 PCB 布局。本應用報告旨在研究 PCB 布局對 LDO 熱性能的影響,為設計人員提供參考。盡管此前已有《采用小型 SMD 封裝的 LDO 熱性能》應用報告 和《AN-1520 確保外露封裝實現出色熱阻的電路板布局布線指南》應用報告 探討過該主題,但本研究通過在功能性場景下采集數據,力求提升結論的實用性。該設置包括帶有無源器件(模擬 TI 評估模塊 (EVM))的功能 PCB 布局以及通過有源供電進行的熱性能測量。有源供電是指將 LDO 置于正常工作狀態,并通過改變輸入電壓與負載電流來增加器件功耗,使器件結區產生熱量。

評估半導體熱性能最常用的參數是結到環境熱阻 θJA。方程式 1 顯示,該參數定義為器件每消耗 1 瓦功率時,器件工作溫度與結溫差值,公式如下:

在特定功耗水平下,設計中 θJA 越小,器件結溫越低,從而可提升器件壽命與可靠性。《半導體和 IC 封裝熱指標》應用報告 指出,對 θJA 影響較大的兩個因素是 PCB 布局與 IC 封裝。TPS745(WSON 封裝)、TPS7B82-Q1(TO-252 封裝)和 TLV755P(SOT-23 封裝)三款 LDO 采用五種不同的 PCB 布局進行了測試,以探究上述兩個因素對熱性能的影響程度。

半導體熱性能受氣流、海拔、環境溫度等多種外部因素影響,因此 JEDEC 需針對 θJA 和其他熱指標制定標準化的測量流程與測試板。為了完成本應用報告的測試,針對每種封裝設計了兩類測試板布局,即 https://www.jedec.org/system/files/docs/JESD51-3.PDF 中介紹的低效導熱性測試板的近似布局和 https://www.jedec.org/system/files/docs/jesd51-7.PDF 中介紹的高有效導熱性測試板的近似布局,除此之外,還額外設計了三種定制化布局。每塊電路板的面積與層疊結構均遵循 JEDEC 標準測試板近似布局:4 層 PCB,面積為 9in2(3 英寸 x 3 英寸)。外層銅箔厚度為 2 盎司,內層銅箔厚度為 1 盎司。為每種封裝制作的五種布局中,與器件相連的銅箔量逐漸增加,此舉旨在測量結到環境熱阻 θJA,并驗證其與銅箔覆蓋率之間的反比關系。為提高三款封裝測試結果的一致性,每種布局中用于散熱的銅箔量均保持一致。按銅箔含量從低到高排序,這些布局類型分別命名為:

- 1S0P 近似布局

- 內部斷開布局

- JEDEC 高 K 近似布局

- 熱增強型

- 熱飽和型

根據 https://www.jedec.org/system/files/docs/JESD51-9.pdf 中規定的 JEDEC 標準,所有 WSON 和 TO-252 布局的散熱焊盤處均設有散熱過孔。這些散熱過孔的直徑為 20 毫米 (mm),孔徑為 10 毫米,銅鍍層厚度為 17 微米。

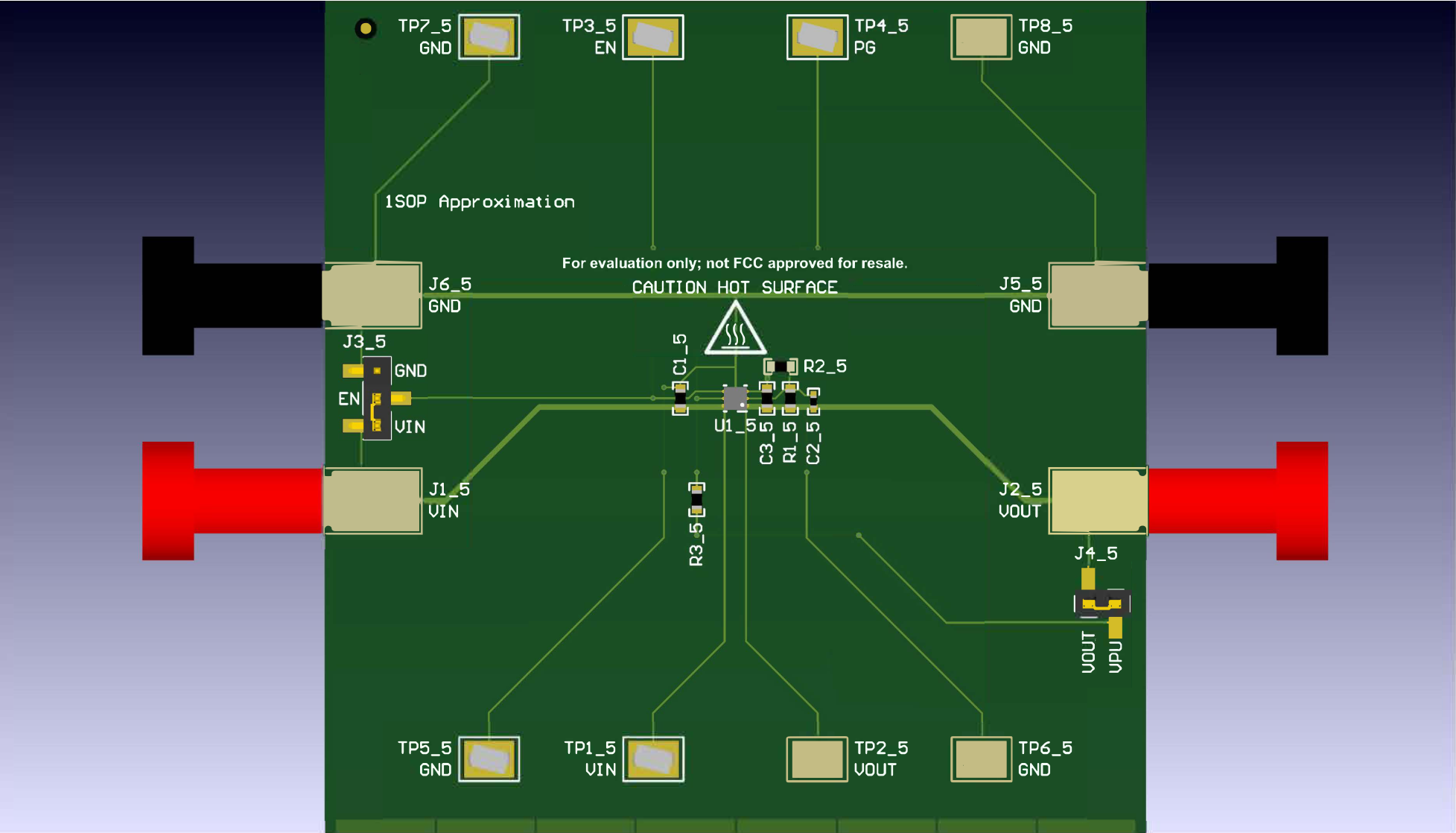

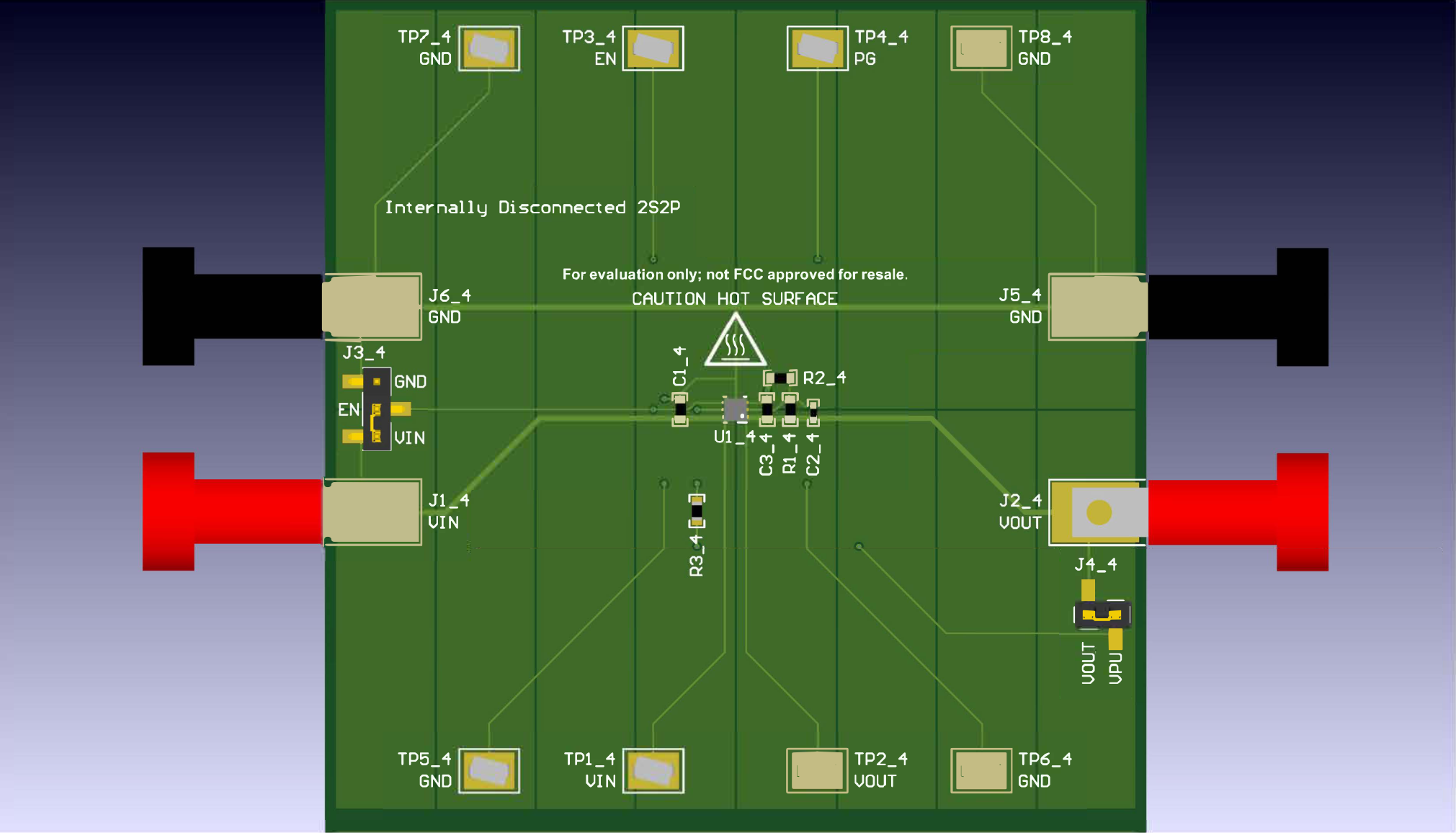

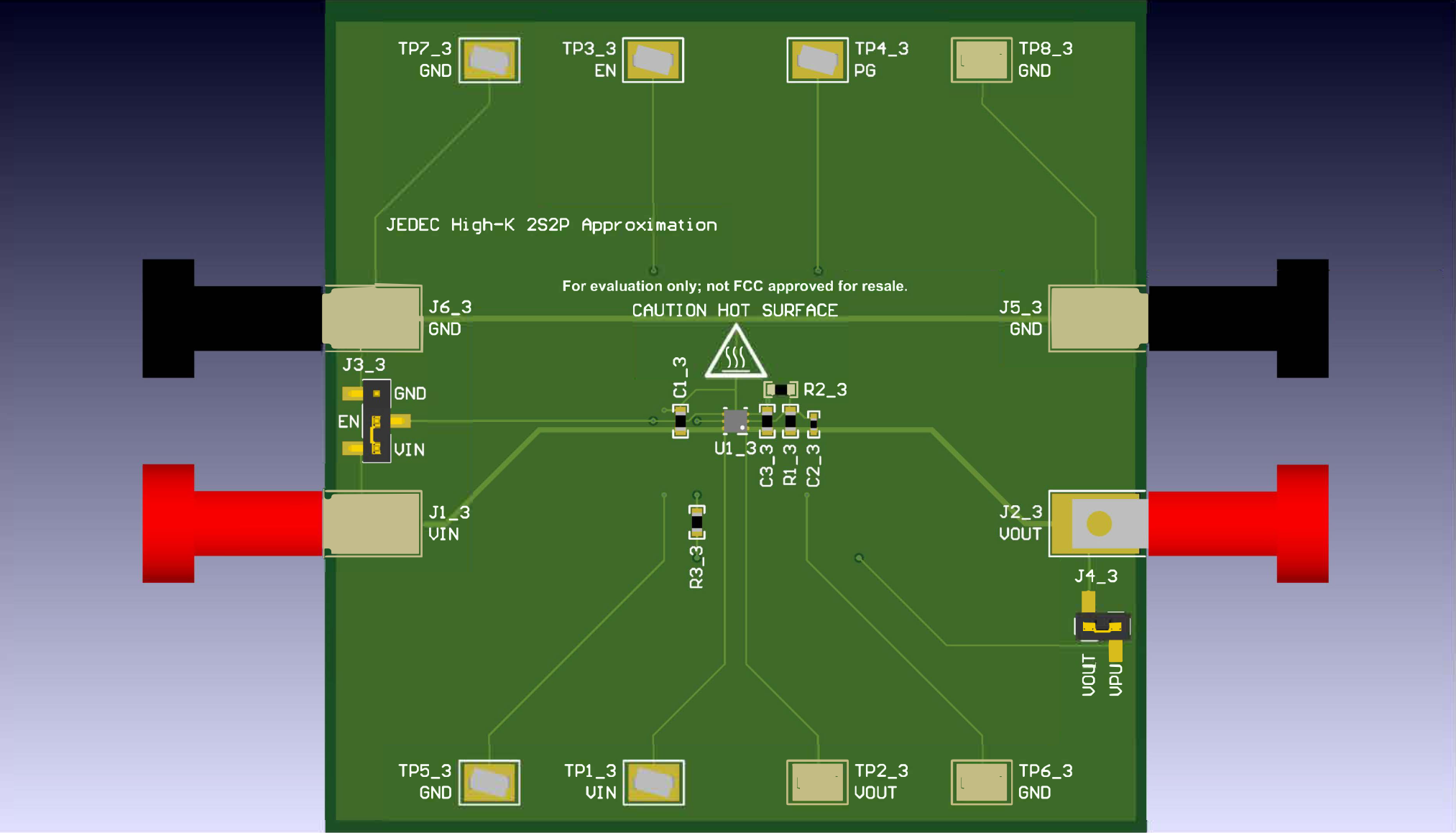

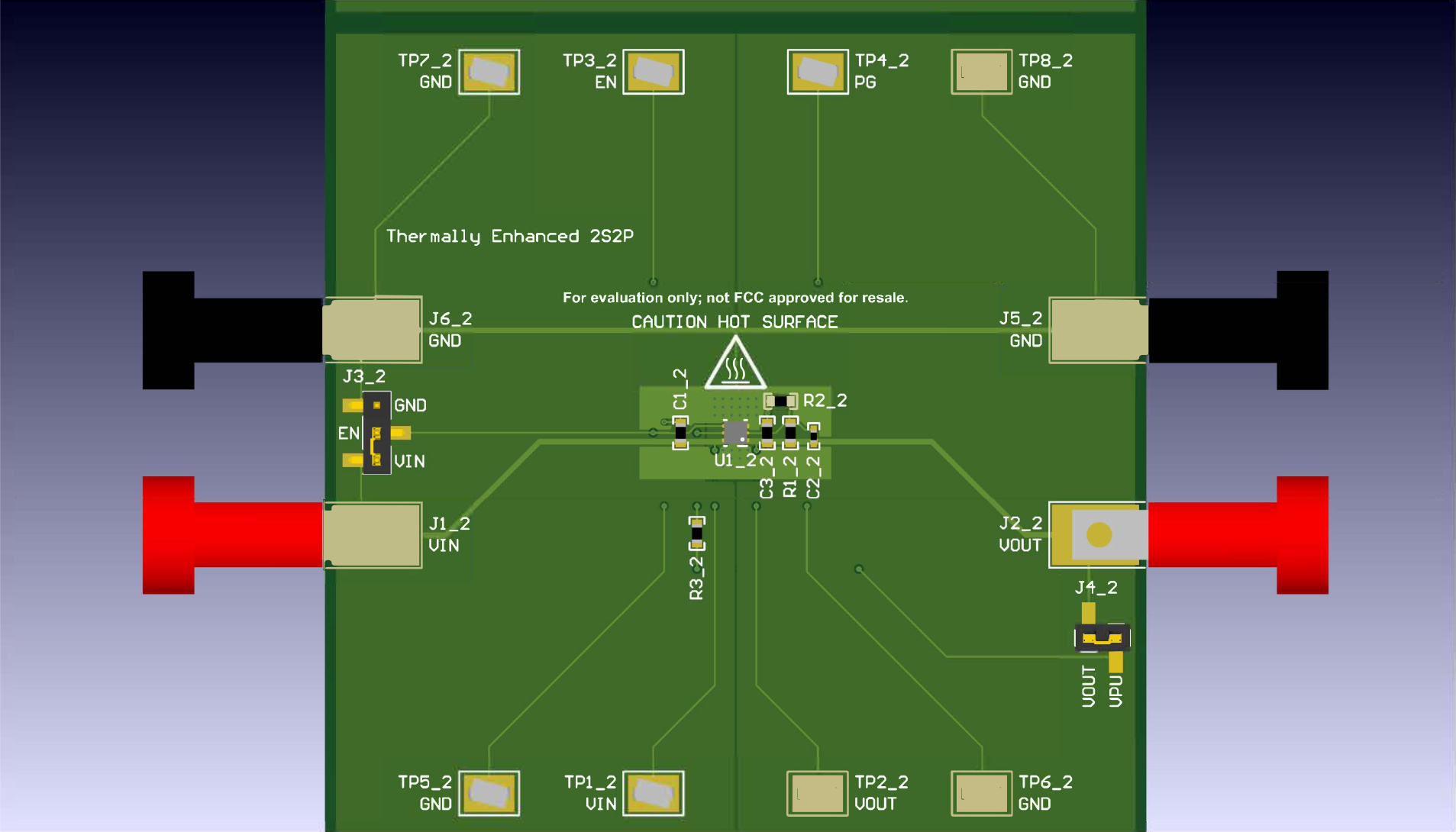

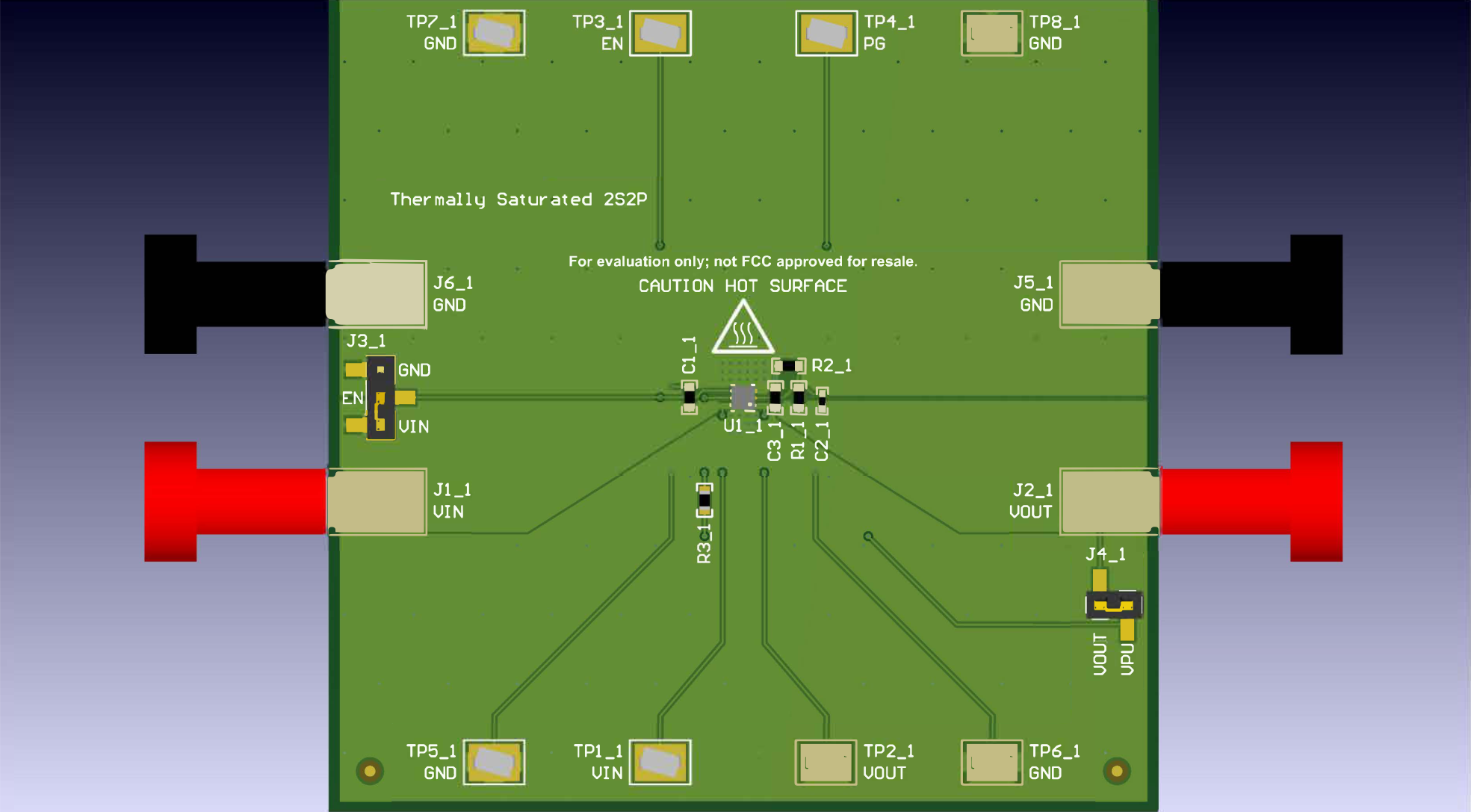

選用兩個不同的 θJA 值作為比較基準。第一種是 θJA, datasheet,該值以 RθJA 形式標注在各器件數據手冊的“熱信息”表格中。θJA, datasheet 通過 JEDEC 高 K 熱量測試板的熱模型推導得出,是設計人員評估熱性能最常用的參數。第二個值為 θJA,1S0P,該值通過 1S0P 近似布局實測得出。此值提供了最壞情況布局的預期熱性能示例。圖 1-1 至圖 1-5 顯示了為采用 WSON 封裝的 TPS745 設計的每個布局所生成的 3D 圖像。每種布局的四層板結構圖可參見AppendixA。表 1-1 提供了每種設計布局和覆銅的說明。

| 電路板 | 屬性 | 說明 | 連接的銅面積 (in2) | 斷開的銅面積 (in2) |

|---|---|---|---|---|

| 1S0P 近似布局 | 頂層 | 僅走線 | 無 | 無 |

| 內層 1 | 無銅 | |||

| 內層 2 | 無銅 | |||

| 底層 | 僅走線 | |||

| 額外的散熱過孔 | 無 | |||

| 內部斷開布局 | 頂層 | 僅走線 | 0.07 | 16.8 |

| 內層 1 | 中等面積、未連接、不連續的銅平面(1) | |||

| 內層 2 | 中等面積、未連接、不連續的銅平面(1) | |||

| 底層 | 走線及一個小型接地平面 | |||

| 額外的散熱過孔 | 無 | |||

| JEDEC 高 K 近似布局 | 頂層 | 僅走線 | 10.2 | 8.53 |

| 內層 1 | 一個較大的接地平面 | |||

| 內層 2 | 走線和一個大的未連接平面 | |||

| 底層 | 一個中等接地平面 | |||

| 額外的散熱過孔 | 無 | |||

| 熱增強型 | 頂層 | 走線及一個小型接地平面 | 10.5 | 8.43 |

| 內層 1 | 小型接地平面及兩個未連接銅平面 | |||

| 內層 2 | 走線及一個中型接地平面 | |||

| 底層 | 一個中等接地平面 | |||

| 額外的散熱過孔 | 僅器件周圍 | |||

| 熱飽和型 | 頂層 | 大型接地平面及電源平面 | 34.1 | 無 |

| 內層 1 | 一個較大的接地平面 | |||

| 內層 2 | 走線及一個大型接地平面 | |||

| 底層 | 一個較大的接地平面 | |||

| 額外的散熱過孔 | 器件周圍和整個 PCB |

圖 1-1 TPS745 (WSON) 1S0P 近似布局

圖 1-1 TPS745 (WSON) 1S0P 近似布局 圖 1-2 TPS745 (WSON) 內部斷開布局

圖 1-2 TPS745 (WSON) 內部斷開布局 圖 1-3 TPS745 (WSON) JEDEC 高 K 近似布局

圖 1-3 TPS745 (WSON) JEDEC 高 K 近似布局 圖 1-4 TPS745 (WSON) 熱增強型布局

圖 1-4 TPS745 (WSON) 熱增強型布局 圖 1-5 TPS745 (WSON) 熱飽和型布局

圖 1-5 TPS745 (WSON) 熱飽和型布局