ZHCSIS3D September 2018 – June 2025 DP83869HM

PRODUCTION DATA

- 1

- 1 特性

- 2 應用

- 3 說明

- 4 Device Comparison

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 WoL (Wake-on-LAN) Packet Detection

- 7.3.2 Start of Frame Detect for IEEE 1588 Time Stamp

- 7.3.3 Clock Output

- 7.3.4 Loopback Mode

- 7.3.5 BIST Configuration

- 7.3.6 Interrupt

- 7.3.7 Power-Saving Modes

- 7.3.8 Mirror Mode

- 7.3.9 Speed Optimization

- 7.3.10 Cable Diagnostics

- 7.3.11 Fast Link Drop

- 7.3.12 Jumbo Frames

- 7.4

Device Functional Modes

- 7.4.1 Copper Ethernet

- 7.4.2 Fiber Ethernet

- 7.4.3 Serial GMII (SGMII)

- 7.4.4 Reduced GMII (RGMII)

- 7.4.5 Media Independent Interface (MII)

- 7.4.6 Bridge Modes

- 7.4.7 Media Convertor Mode

- 7.4.8 Register Configuration for Operational Modes

- 7.4.9 Serial Management Interface

- 7.4.10

Auto-Negotiation

- 7.4.10.1 Speed and Duplex Selection - Priority Resolution

- 7.4.10.2 Leader and Follower Resolution

- 7.4.10.3 Pause and Asymmetrical Pause Resolution

- 7.4.10.4 Next Page Support

- 7.4.10.5 Parallel Detection

- 7.4.10.6 Restart Auto-Negotiation

- 7.4.10.7 Enabling Auto-Negotiation Through Software

- 7.4.10.8 Auto-Negotiation Complete Time

- 7.4.10.9 Auto-MDIX Resolution

- 7.5

Programming

- 7.5.1

Strap Configuration

- 7.5.1.1 Straps for PHY Address

- 7.5.1.2 Strap for DP83869HM Functional Mode Selection

- 7.5.1.3 LED Default Configuration Based on Device Mode

- 7.5.1.4 Straps for RGMII/SGMII to Copper

- 7.5.1.5 Straps for RGMII to 1000Base-X

- 7.5.1.6 Straps for RGMII to 100Base-FX

- 7.5.1.7 Straps for Bridge Mode (SGMII-RGMII)

- 7.5.1.8 Straps for 100M Media Convertor

- 7.5.1.9 Straps for 1000M Media Convertor

- 7.5.2 LED Configuration

- 7.5.3 Reset Operation

- 7.5.1

Strap Configuration

- 7.6 Register Maps

-

8 Application and Implementation

- 8.1 Application Information

- 8.2 Typical Applications

- 8.3 Power Supply Recommendations

- 8.4 Layout

- 9 Device and Documentation Support

- 10Revision History

- 11Mechanical, Packaging, and Orderable Information

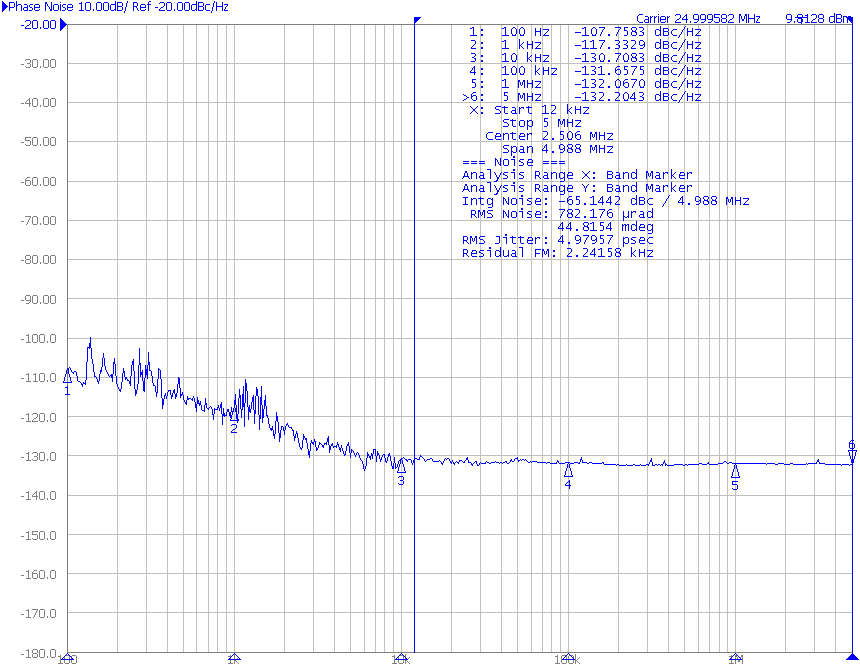

8.2.1.2.1.3 Clock Out (CLK_OUT) Phase Noise

Figure 8-4 provides a phase noise plot for the 25MHz clock output from the device.

Note: The phase noise on the CLK_OUT pin before linkup and after link up with no packets being generated are expected to be lower than pictured.

Figure 8-4 25MHz Clock Output Phase Noise