ZHCAFO9 August 2025 TLC69601-Q1 , TLC69604-Q1

3.3 TXFIFO 配置

TXFIFO 配置

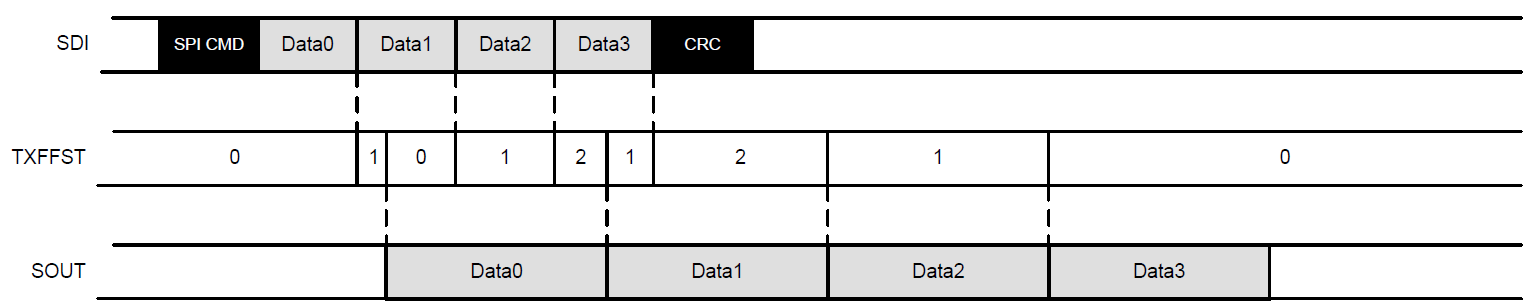

TLC69699-Q1 具有傳輸和接收 FIFO,這意味著傳輸 FIFO (TXFIFO) 是由 SPI 外設接收并由 CCSI 控制器傳輸的數據。兩個 FIFO 都是 16 位寬的先入先出存儲器緩沖區。FIFO 用于存儲數據字,以滿足數據在 SPI 時鐘域和 CCSI 時鐘域之間傳輸時的時序要求。當 SPI 時鐘域以高于 CCSI 時鐘域的頻率運行時,TXFIFO 會存儲尚未由 CCSI 控制器傳輸的 SPI 外設接收到的數據。計數器 (TXFFST) 會跟蹤當前存儲在 TXFIFO 中的字數,最大 TXFFST 值可設置為 0x1FF。圖 3-5 中描述了 SPI 外設以高于 CCSI 控制器的時鐘頻率運行的示例,只要正確防止 FIFO 溢出,就會設置一個低于 SPI 頻率的 CCSI 頻率。

圖 3-5 以高于 CCSI 控制器的頻率運行的 SPI 外設示例

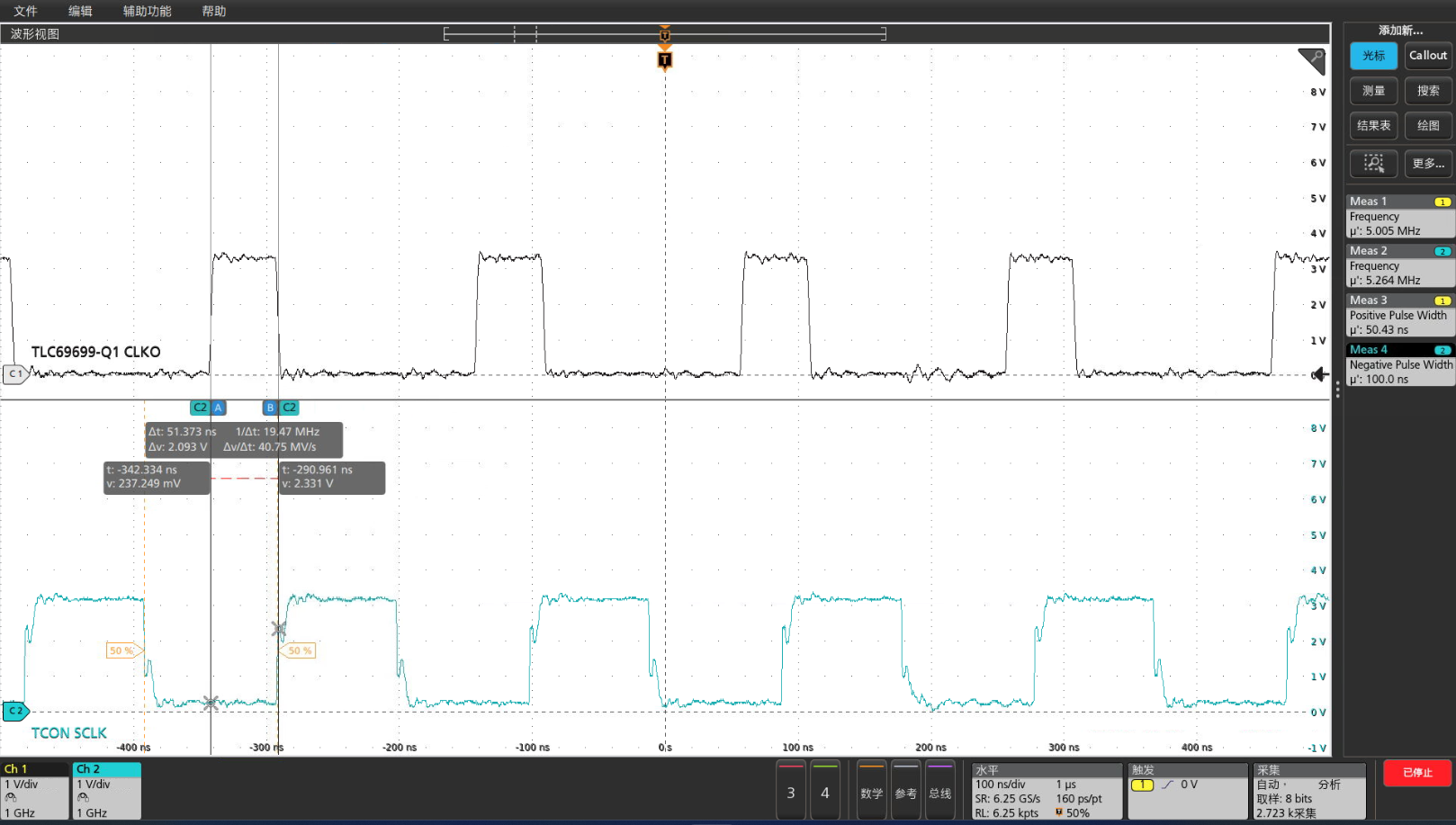

圖 3-5 以高于 CCSI 控制器的頻率運行的 SPI 外設示例TCON 現在可以將 SPI 頻率從 8MHz 降低到 5.2MHz,TLC69699-Q1 TXFIFO 有助于進一步將 CCSI 頻率降低到 5MHz 或更低,如圖 3-6 所示,底部波形是 5.2MHz 時的 TCON SPI 輸出,頂部是 5MHz 時的 TLC69699-Q1 CCSI 輸出。只要正確防止 FIFO 溢出,就可以使用 CCSI_DATA_RATE 為 TLC69699-Q1 設置較低的 CCSI 輸出頻率。

圖 3-6 使用 TXFIFO 進行 TLC69699-Q1 輸入和輸出頻率控制

圖 3-6 使用 TXFIFO 進行 TLC69699-Q1 輸入和輸出頻率控制