ZHCAF09E July 1994 – July 2021

6 總線保持電路

要為懸空的總線提供已定義的電平,最有效的方法是在特定系列上使用德州儀器 (TI?) 內置總線保持功能,或者作為外部元件(如 SN74ACT1071 和 SN74ACT1073)(見 表 6-1)。

| 器件類型 | 帶有總線保持功能 |

|---|---|

| SN74ACT1071 | 帶有鉗位二極管的 10 位總線保持功能 |

| SN74ACT1073 | 帶有鉗位二極管的 16 位總線保持功能 |

| ABT Widebus+(32 位和 36 位) | 所有器件 |

| ABT 八進制和 Widebus | 僅限特定器件 |

| AHC/AHCT Widebus | TBA(僅限特定器件) |

| 低電壓(LVT 和 ALVC) | 所有器件 |

| LVC Widebus | 所有器件 |

特定 TI 系列中使用了總線保持電路,以幫助解決懸空輸入問題,并消除對上拉和下拉電阻器的需求。總線保持電路由兩個背對背反相器組成,輸出通過電阻器反饋到輸入端(見 圖 6-1)。要了解總線保持電路的工作原理,請假設有源驅動器已將線路切換至高電平。這會導致沒有電流流過反饋電路。現在,驅動器進入高阻抗狀態,總線保持電路通過反饋電阻器保持高電平。總線保持電路的電流要求僅取決于電路的泄漏電流。當總線處于低電平狀態然后變為無效時,同樣的情況也適用。

圖 6-1 典型總線保持電路

圖 6-1 典型總線保持電路如本節前面所述,TI 提供作為獨立的 10 位和 16 位器件(SN74ACT1071 和 SN74ACT1073)的總線保持功能,具有連接到 VCC 和 GND 的鉗位二極管,以防止由于總線上的阻抗不匹配引起線路反射。由于在 CMOS 電路中無法輕松實現純歐姆電阻器,因此將一種稱為傳輸門的配置用作反饋元件(見 圖 6-2)。在緩沖級的輸入和輸出之間并聯了一個 N 溝道和一個 P 溝道。N 溝道晶體管的柵極連接到 VCC,P 溝道的柵極連接到 GND。當緩沖器的輸出為高電平時,P 溝道開啟,而當輸出為低電平時,N 溝道開啟。兩個溝道的表面積都相對較小,漏極到源極的導通狀態電阻 Rdson 約為 5kΩ。

圖 6-2 獨立總線保持電路 (SN74ACT107x)

圖 6-2 獨立總線保持電路 (SN74ACT107x)假設在實際應用中,總線上驅動器的泄漏電流為 IOZ = 10mA,5kΩ 電阻兩端的壓降為 VD = 0.8V(假設此值是為了確保達到定義的邏輯電平)。然后,一個總線保持電路能夠處理的最大元件數量可通過 方程式 6 計算:

74ACT1071 和 74ACT1073 還提供鉗位二極管,作為總線保持電路的一項附加功能。這些二極管用于鉗制由線路反射產生的任何過沖或下沖。圖 6-3 和圖 6-4 顯示了輸入電壓高于 VCC 或低于 GND 時二極管的特性。在 VI = –1V 時,二極管可以提供約 50 mA,這有助于消除下沖。當需要考慮總線噪聲問題時,這會非常有用。

| VCC = 5V |

| VCC = 5V |

TI 還提供總線保持電路,作為某些高級系列驅動器和接收器的新增功能。此電路與獨立電路類似,在第二個逆變器的漏極上添加了一個二極管(僅限 ABT 和 LVT ,見 圖 6-5)。當輸入電壓高于 VCC (VI > VCC) 時,二極管會阻斷過沖電流,因此僅存在泄漏電流。這個電路使用器件的輸入級作為它的第一個反相器;第二個反相器會創建反饋特性。總線保持電路可以處理的最大元件數量的計算方式與前一個示例類似。然而,此電路相對于獨立總線保持電路的優勢在于,它無需外部元件或電阻,因而可以減少占用的電路板面積。這對于某些設計至關重要,尤其是在使用寬總線時。此外,由于成本和電路板尺寸限制是主要問題,設計人員更傾向于采用簡便的解決辦法:即使用可直接插入更換的部件。TI 在多個系列中提供此功能(有關更多詳細信息,請見 表 6-1)。

圖 6-5 具有總線保持電路的 ABT/LVT 和 ALVC/LVC 系列的輸入結構

圖 6-5 具有總線保持電路的 ABT/LVT 和 ALVC/LVC 系列的輸入結構圖 6-6 和 圖 6-7 顯示了當輸入電壓從 0V 掃描到 5V 時,總線保持電路在 3.3V 和 5V 工作電壓下的輸入特性。這些特性在行為上與弱驅動器類似。當輸入為低電平時,該驅動器將電流灌入器件,而當輸入為高電平時,則從器件中拉出電流。當電壓接近閾值時,電路會嘗試切換到另一狀態,始終將輸入保持在有效電平。這是使用內部反饋電路的結果。該圖還顯示,當輸入接近閾值時,電流處于最大值。輸入電壓為 3.3V 時,II(hold) 最大值約為 25mA,輸入電壓為 5V 時,最大值約為 400mA。

圖 6-6 VO—輸出電壓—V 總線保持輸入特征

圖 6-6 VO—輸出電壓—V 總線保持輸入特征 圖 6-7 VI—輸入電壓—V 總線保持輸入特性

圖 6-7 VI—輸入電壓—V 總線保持輸入特性當具有總線保持電路的多個器件由單個驅動器驅動時,可能會擔心驅動器的交流開關能力會變弱。作為小型驅動器,總線保持電路在開關時需要用到交流電流。使用 TI CMOS 和 BiCMOS 系列時,該電流不大。圖 6-8 顯示了驅動六個 LVTH16244 器件的 4mA 緩沖器。布線是 75Ω 傳輸線。接收器間距 1cm,驅動器位于布線中心。圖 6-9 和圖 6-10 顯示了當連接到六個切換到低電平或高電平的接收器時,總線保持負載對驅動器的影響。圖 6-9 和圖 6-10 還顯示了總線保持電路與接收器斷開連接時的同一系統。這兩張圖都顯示了總線保持對驅動器上升和下降時間的影響。最初,總線保持電路會試圖抵消驅動器,從而增加上升或下降時間。然后,總線保持電路改變狀態(注意交叉點),這有助于驅動器更快地開關,從而減少上升或下降時間。

圖 6-8 驅動器和接收器系統

圖 6-8 驅動器和接收器系統

| VCC = 3.3V | TA = 25°C |

| VCC = 3.3V | TA = 25°C |

圖 6-11 顯示了輸入從 0V 掃描到 5V 時總線保持電路的電源電流 (ICC)。VI 約為 1.5V 時的尖峰是由 N 溝道和 P 溝道同時導通導致的。這是 CMOS 晶體管的特性之一。

| VCC = 5V |

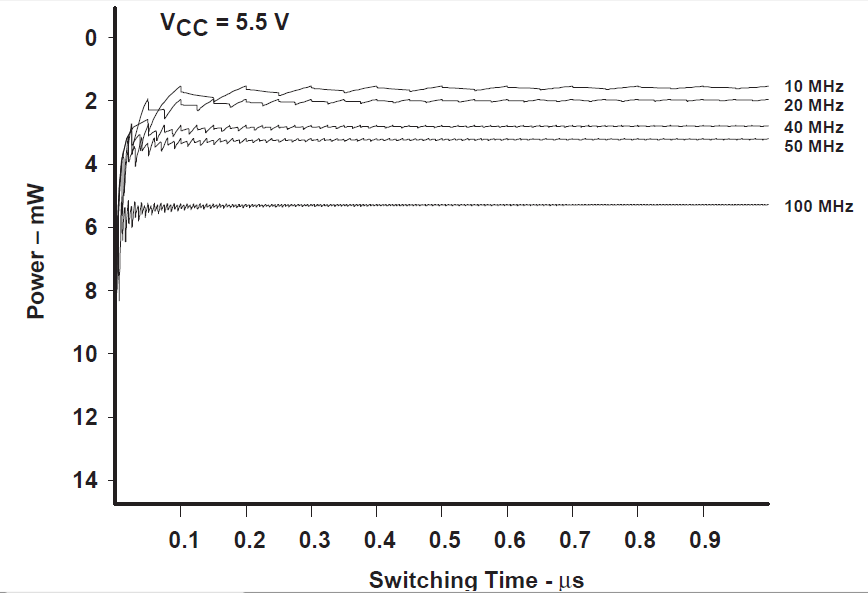

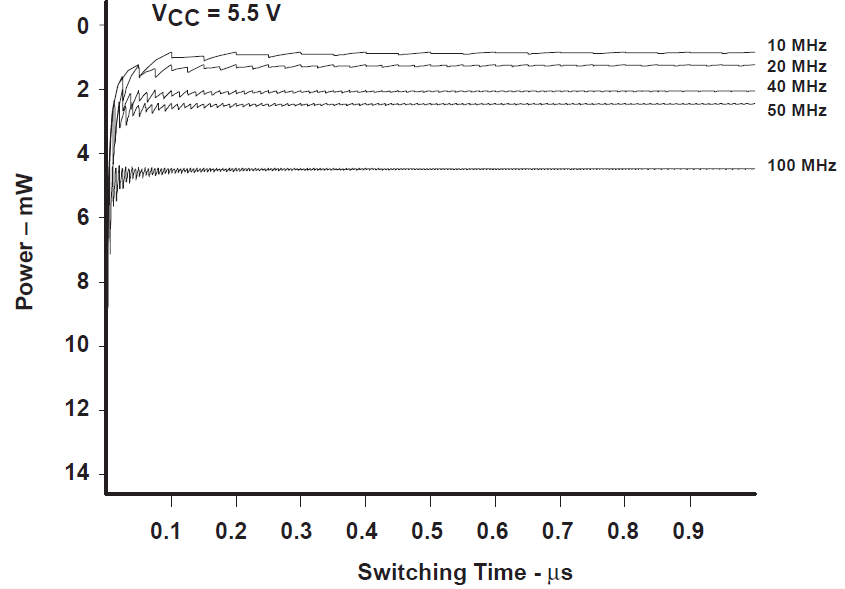

以較高頻率切換輸入時,總線保持電路的功耗極低。圖 6-12 和 圖 6-13 顯示了輸入在不同頻率下(具有或不具有總線保持功能)消耗的功率。總線保持電路在較高頻率下的功耗雖然會有所增加,但并不足以在功率計算中予以考慮。

圖 6-12 不同頻率下的輸入功率圖(使用總線保持電路時)

圖 6-12 不同頻率下的輸入功率圖(使用總線保持電路時) 圖 6-13 不同頻率下的輸入功率圖(不使用總線保持電路時)

圖 6-13 不同頻率下的輸入功率圖(不使用總線保持電路時)表 6-2 示了數據表中總線保持電路的直流規范。第一個測試條件是將總線保持在 0.8V 或 2V 所需的最小電流。這些電壓滿足 TTL 輸入所指定的低電平和高電平。第二個測試條件是總線保持電路在 0V 至 3.6V(針對低壓系列)或 0V 至 5.5 V(針對 ABT)之間的任意輸入電壓下,所拉取或灌入的最大電流。隨著輸入電壓接近電源軌電壓,總線保持電流變得很小。對于具有總線保持功能的收發器而言,輸出泄漏電流 IOZH 和 IOZL 無關緊要,因為由于存在總線保持電路,無法執行真正的泄漏測試。由于總線保持電路充當小型驅動器,因此它往往會拉取或灌入與泄漏電流方向相反的電流。這個情況只適用于具有總線保持功能的收發器,而不適用于緩沖器。所有 LVT、ABT Widebus+ 以及特定的 ABT 八進制和 Widebus 器件,均具有總線保持功能(有關更多信息,請見 表 6-1 或與當地的 TI 銷售辦事處聯系)。

| 最小值 | 最大值 | 單位 | |||||

|---|---|---|---|---|---|---|---|

| II(hold) | 數據輸入或 I/O | LVT、LVC、ALVC | VCC = 3V | VI = 0.8V | 75 | μA | |

| VI = 2V | -75 | ||||||

| LVC、ALVC | VCC = 3.6V | VI = 0 至 3.6V | ±500 | ||||

| ABT Widebus+和特定的 ABT | VCC = 4.5V | VI = 0.8V | 100 | ||||

| VI = 2V | -100 | ||||||

| IOZH/IOZL | 具有總線保持功能的收發器 | ABT | 此測試不是真正的 IOZ 測試,因為總線保持功能在 I/O 引腳上始終處于活動狀態。總線保持電路提供的電流往往與輸出泄漏電流的方向相反。 | ±1 | μA | ||

| LVT、LVC、ALVC | |||||||

| 具有總線保持功能的緩沖器 | ABT | 測試是真正的 IOZ 測試,因為輸出引腳上不存在總線保持功能。 | ±10 | ||||

| LVT、LVC、ALVC | ±5 | ||||||