ZHCABM9B May 2022 – November 2023 TPS62860 , TPS62861 , TPS62864 , TPS62866 , TPS62868 , TPS62869 , TPS62870-Q1 , TPS62871-Q1 , TPS62872-Q1 , TPS62873-Q1 , TPS6287B10 , TPS6287B15 , TPS6287B20 , TPS6287B25 , TPSM8287A06 , TPSM8287A10 , TPSM8287A15 , TPSM8287B30

4 運行期間動態輸出電壓調整

I2C 接口支持在運行期間調整輸出電壓。通常采用一個或多個 I2C 寄存器設置輸出電壓,并且可以在運行期間直接重新寫入這些寄存器。一些器件還包含 VID 或 VSEL 引腳,用于在兩個或更多輸出電壓之間切換。在這種情況下,仍可以在運行期間根據需要重新寫入這些寄存器,也可以對這些寄存器一次寫入至特定的工作電壓。

例如,LPDDR5 DRAM VDDQ 電源軌可以設置為 0.5V 或 0.3V。通過重寫 I2C 寄存器以更改輸出電壓,或使用 VID 引腳更改為具有不同輸出電壓的不同 I2C 寄存器,可以實現此電壓更改。LPDDR5 DRAM 與前幾代相比,提供了額外的節能效果。在空閑狀態下,此時 LPDDR5 DRAM 處于低功耗工作狀態中,存儲器控制器可以使用 LPDDR5 DRAM 的動態電壓和頻率縮放 VDDQ (DVFSQ) 功能同時降低電源電壓和工作頻率。

圖 4-1 顯示了為 LPDDR5 存儲器供電的典型方框圖,在 VDDQ 電源軌上進行了動態輸出電壓調整。

圖 4-1 TPS62869 為 LPDDR5 DRAM 上的所有電源軌供電,并在 VDDQ 電源軌上進行動態輸出電壓調整

圖 4-1 TPS62869 為 LPDDR5 DRAM 上的所有電源軌供電,并在 VDDQ 電源軌上進行動態輸出電壓調整系統設計確定是否將使用雙電源軌模式來實現額外的節能。與 VDDQ 電源軌(可動態更改)不同,VDD2H/L 始終在固定電壓下運行,無論是使用單電源軌還是雙電源軌模式。

TPS62869 提供不同的電壓斜坡速度,使系統工程師能夠為 DVFSQ 由低電平到高電平轉換選擇正確的條件。例如,如果在 VDDQ 恢復到 0.5V 標稱水平,以進行高速運行時需要快速響應,TPS62869 可以將其電壓斜坡速度從 1mV/us 調整到 20mV/us。

表 4-1 顯示 DVFSQ 轉換的最大 VDDQ 斜坡速率。

| VDDQ 壓擺率 | 最大值 | 單位 |

|---|---|---|

| 快速響應模式 (大電流) | 20 | mV/us |

| 正常運行 (默認) | 4,8 | mV/us |

此外,可以啟用操作參數(例如輸出電壓變化期間的強制 PWM 模式),以滿足 VDDQ 由低電平到高電平轉換期間的嚴格定時要求。這樣可在較低的工作狀態下進行快速轉換,并可防止輸出級的緩慢放電,以限制低負載條件下的電壓斜坡速度。

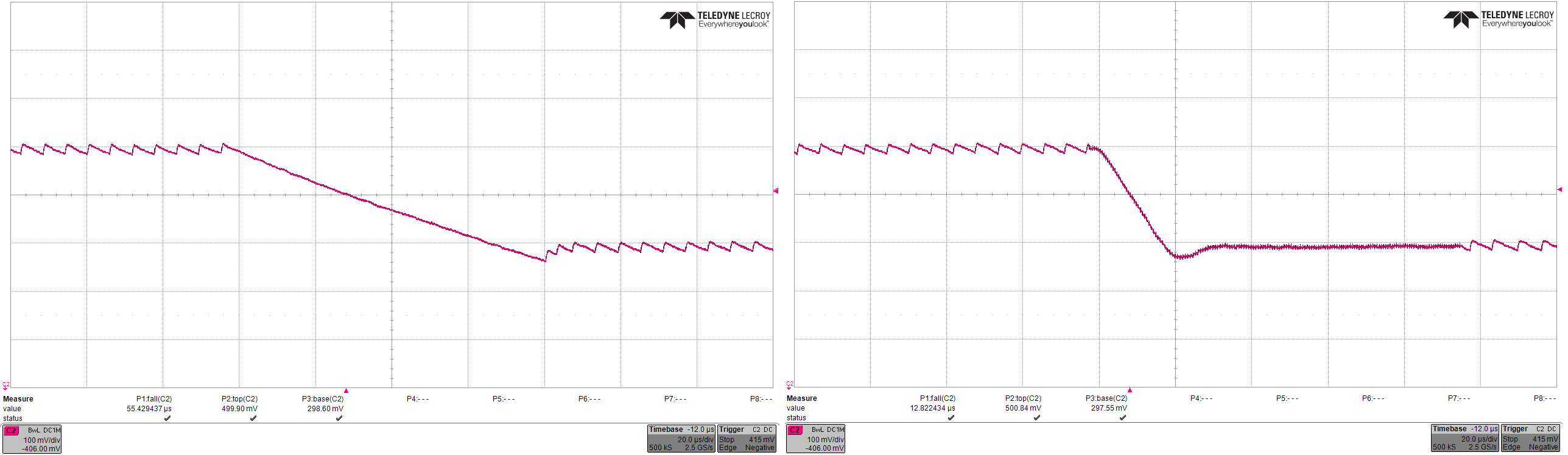

圖 4-2 顯示了在 100mA 負載條件下輸出電壓變化期間,采用和不采用強制 PWM 模式時的 0.5V 至 0.3V 轉換示例。

圖 4-2 20mV/us 壓擺率下的 0.5V 至 0.3V 輸出轉換,IOUT = 100mA,在啟用更改期間不采用 FPWM 模式(左)和采用 FPWM 模式(右)

圖 4-2 20mV/us 壓擺率下的 0.5V 至 0.3V 輸出轉換,IOUT = 100mA,在啟用更改期間不采用 FPWM 模式(左)和采用 FPWM 模式(右)