ZHCT935 May 2025 ADC32RF52 , ADC32RF54 , ADC32RF55 , ADC34RF52 , ADC34RF55 , ADC34RF72 , ADC3548 , ADC3549 , ADC3568 , ADC3569 , ADC3648 , ADC3649 , ADC3668 , ADC3669

6 理論示例:利用抽取功能規劃頻率

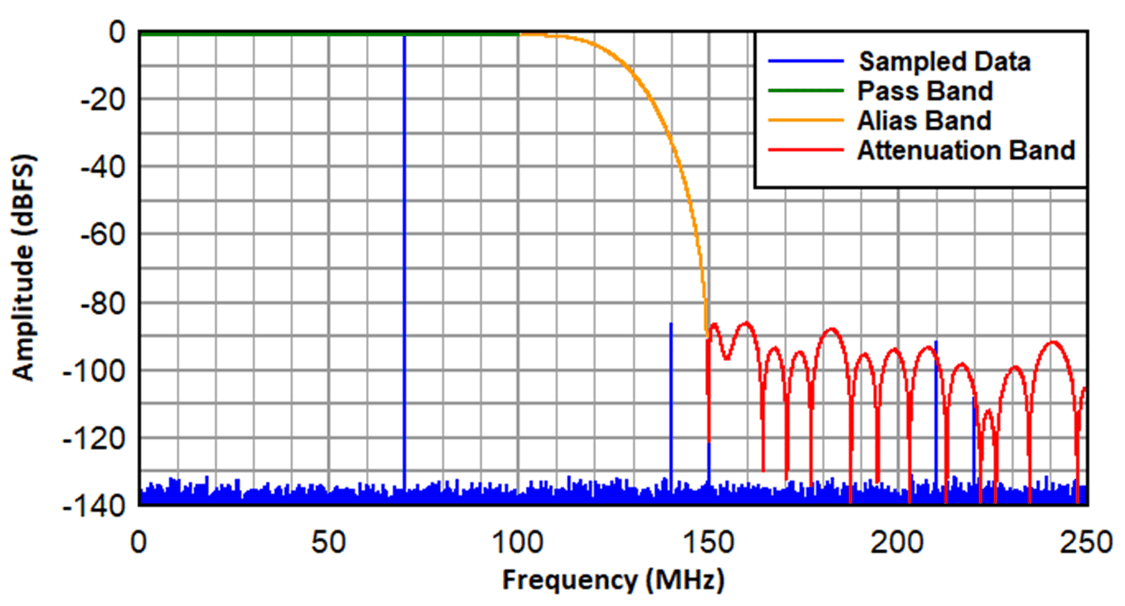

考慮交錯 ADC 以 Fs 采樣一個常規射頻輸入信號。交錯過程會在 Fs/2-Fin 處引入偽波,可能會干擾預期信號。通過應用 2 倍抽取濾波器(如 圖 4 所示),可以將此偽波衰減到抽取濾波器的抑制限值范圍內。此外,抽取過程可降低 ADC 的輸出數據速率,從而實現具有成本效益的 FPGA 連接并簡化下游處理。此外,由于 SNR 中的 N(即噪聲)減半,而 S(即信號)保持不變,寬帶噪聲的降低會帶來約 3dB 的過程增益。

圖 4 500MSPS 且 70MHz FIN(抽取因子為 2)條件下理論數據的抽取濾波器響應。

圖 4 500MSPS 且 70MHz FIN(抽取因子為 2)條件下理論數據的抽取濾波器響應。