ZHCAEV7 December 2024 LSF0101 , LSF0102 , LSF0108 , LSF0204

3 在推挽應(yīng)用中使用 LSF 時(shí)是否需要上拉電阻器?

由于開漏驅(qū)動(dòng)器只能將總線拉至低電平,因此當(dāng)與開漏接口配合使用時(shí),需要使用上拉電阻器將總線驅(qū)動(dòng)至邏輯高電平狀態(tài)。但是,當(dāng) LSF 與推挽驅(qū)動(dòng)器一起使用時(shí),這項(xiàng)要求就不那么明確了。

圖 3-1 推挽和開漏配置中均使用 LSF 的示例原理圖

圖 3-1 推挽和開漏配置中均使用 LSF 的示例原理圖| 升壓轉(zhuǎn)換 (1.2V) → (3.3V) | 降壓轉(zhuǎn)換 (3.3V) → (1.2V) | |||

|---|---|---|---|---|

| 輸入/輸出 (I/O) | A3 (I) | B3 (O) | B2 (I) | A2 (O) |

| 是否需要上拉電阻器? | 否 | 推薦 | 否 | 如果輸出側(cè)的漏電流過大,或者要轉(zhuǎn)換為另一個(gè)非 VREFA 的電壓,則建議使用上拉電阻器 |

以降壓轉(zhuǎn)換用例(上面原理圖中的 A2/B2)為例,如果觀察到過大的漏電流,則建議在輸出側(cè)(A 側(cè))使用上拉電阻器。當(dāng)接收器嘗試消耗的電流大于內(nèi)部 FET 在邏輯高電平狀態(tài)期間可提供的電流時(shí),就會(huì)發(fā)生這種情況。發(fā)生這種情況時(shí),隨著源極和柵極電壓差變得更大 (VGS> VTH),輸出側(cè)的電壓會(huì)由于內(nèi)部 FET 導(dǎo)通(轉(zhuǎn)換到線性區(qū)域)而下降。這進(jìn)而將總線拉至低電平,導(dǎo)致器件返回上游出現(xiàn)錯(cuò)誤的邏輯低電平信號(hào)。為了解決這個(gè)問題,我們使用外部上拉電阻器來偏移漏電流,以便 FET 可以在發(fā)送邏輯高電平信號(hào)期間保持在截止?fàn)顟B(tài) (VGS<VTH)。在下面的降壓轉(zhuǎn)換仿真中,我們模擬了輸出側(cè)的漏電流,測(cè)量了 VOH 電平并將其與使用上拉電阻器時(shí)的 VOH 電平進(jìn)行了比較。

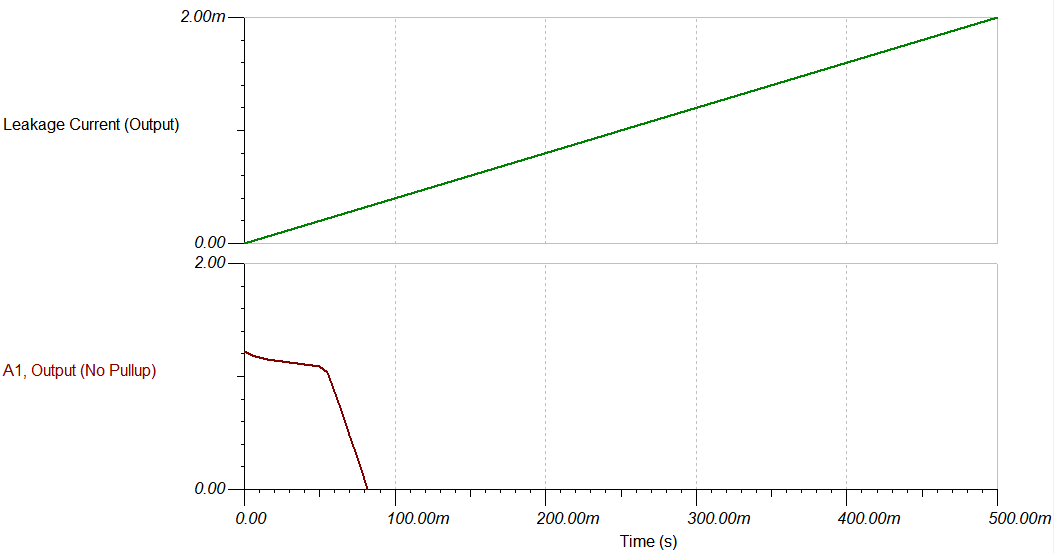

仿真 1:降壓轉(zhuǎn)換期間接收器側(cè)漏電流過大的影響。

在圖 3-2 中,我們使用輸出側(cè)的電流源 (IG1) 來仿真接收器側(cè)的漏電路徑。IG1 處電流的階躍函數(shù)以線性方式增加,于是測(cè)量出輸出側(cè)的電壓。

圖 3-2 接收器側(cè)漏電流過大的仿真設(shè)置

圖 3-2 接收器側(cè)漏電流過大的仿真設(shè)置 圖 3-3 接收器側(cè)漏電流過大的仿真結(jié)果

圖 3-3 接收器側(cè)漏電流過大的仿真結(jié)果隨著輸出漏電流 (IG1) 的增大,觀察到的輸出電壓開始進(jìn)一步下降,直到輸出電壓漂移至閾值電壓以下。到目前為止,輸出電壓與柵極電壓的差值變得足夠大,使得低側(cè)(A 側(cè))成為源極,因此 FET 轉(zhuǎn)換回線性區(qū)域。一旦 FET 在線性區(qū)域運(yùn)行,B 側(cè)(輸入側(cè))的上拉電阻器便開始將電流拉入 A 側(cè),其中的向下斜率可以建模為 VG-VTH/RPUB。請(qǐng)注意,仿真中顯示的數(shù)據(jù)僅用于演示器件在此環(huán)境中的行為。器件的實(shí)際行為取決于多種因素(工藝、變化、溫度等),因此不能保證各項(xiàng)漏電流參數(shù)下的電壓驟降會(huì)有這么小。

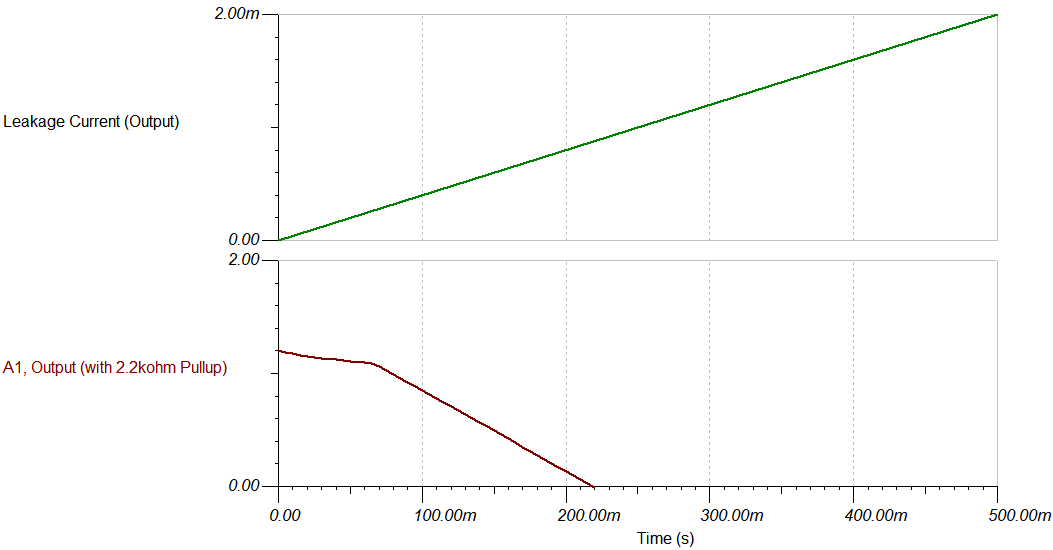

仿真 2:在接收器側(cè)安裝上拉電阻器 (2.2kΩ) 并在接收器側(cè)產(chǎn)生過大漏電流的好處:

圖 3-4 接收器側(cè)安裝上拉電阻器和漏電流過大的仿真設(shè)置

圖 3-4 接收器側(cè)安裝上拉電阻器和漏電流過大的仿真設(shè)置仿真 2:A 側(cè)安裝外部上拉電阻器 (2.2kΩ) 時(shí)的低側(cè)輸出電平

圖 3-5 仿真 2 結(jié)果

圖 3-5 仿真 2 結(jié)果| 輸出側(cè)仿真的漏電流 IG1 (μA) | 輸出電壓 (V),A1 無外部上拉電阻器 | 輸出電壓 (V),A1 帶外部上拉電阻器 |

|---|---|---|

| 10 | 1.19 | 1.2 |

| 100 | 1.13 | 1.14 |

| 200 | 1.09 | 1.11 |

| 250 | 1.01 | 1.09 |

| 275 | 0.53 | 1.07 |

| 300 | 0.28 | 1.03 |

注意:從仿真中獲取的值僅用于演示在輸出側(cè)使用和不使用上拉電阻器情況下漏電流的行為以及對(duì)輸出電壓的影響。

在第二個(gè)原理圖/仿真中,可以使用 A 側(cè)的外部上拉電阻器 (RPUA),通過拉取 A 側(cè)器件能夠灌入/拉出的電流來幫助調(diào)節(jié)電壓。