ZHCADT8A December 2023 – June 2024 TAA5212 , TAC5111 , TAC5112 , TAC5211 , TAC5212 , TAD5112 , TAD5212

3.3.2 帶有錄制功能的默認(rèn)模式(主 Fs - 較高速率)

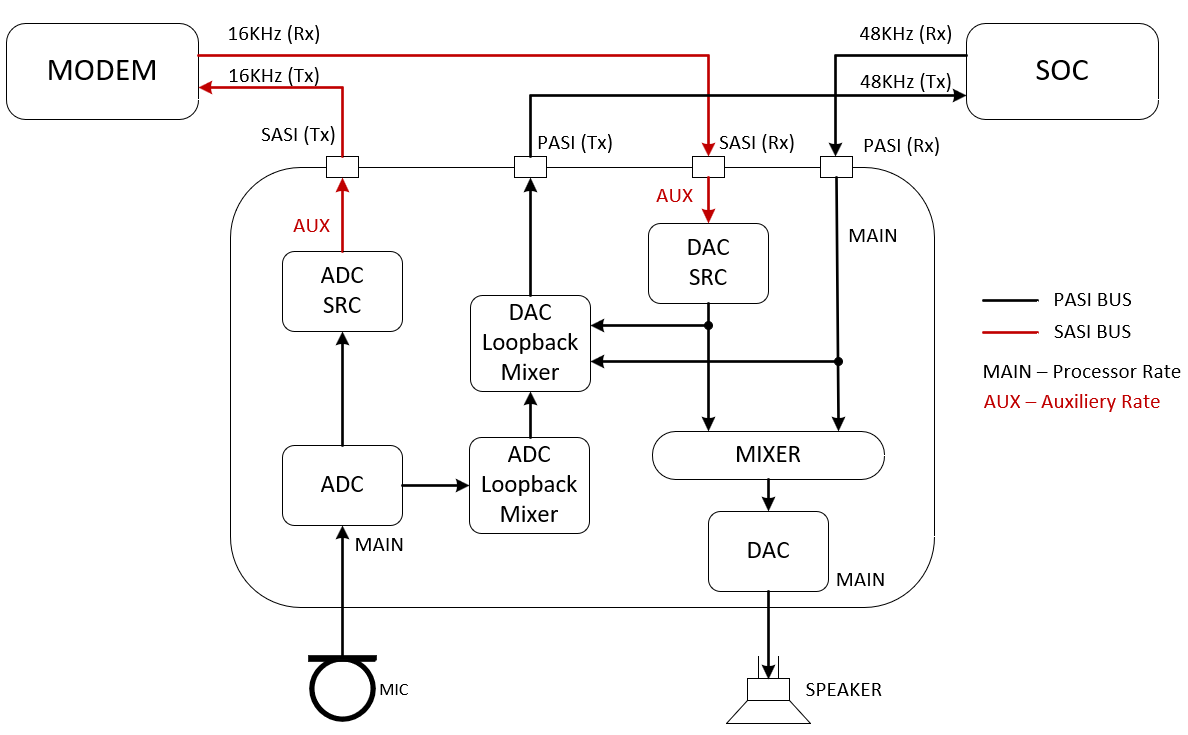

圖 3-6 顯示了該用例的方框圖。PASI 以 48 KHz 運行,SASI 以 16 KHz 運行。在該用例中,模擬輸入(MIC) 以主 Fs 進(jìn)行采樣,并使用 SRC 進(jìn)行下采樣,以降低 SASI 的速率。PASI TX 是采樣的 MIC 輸入與 SASI RX 或 PASI RX 的混合信號。在 DAC 側(cè),SASI RX 數(shù)據(jù)可以在 DAC 輸出(揚聲器)之前與 PASI RX 數(shù)據(jù)進(jìn)行混頻。

圖 3-6 具有錄制功能的默認(rèn)模式圖

圖 3-6 具有錄制功能的默認(rèn)模式圖下文顯示了 PASI 和 SASI 的 Audio Precision APx555 配置。在該測試用例中,混頻器系數(shù)保持為默認(rèn)值(滿量程),輸入電平會被調(diào)整為不超過允許的最大電平(例如 -9dBrG),而不是 0dBrG。

|

PASI APx555: 發(fā)生器: 模擬輸出 (MIC):1KHz 正弦波,-9dBrG (0dBrG = 2Vrms) 分析器: 輸入 1:PASI Tx 的數(shù)字音頻,其中 Fs = 48 KHz、32 位深度 輸入 2:DAC 輸出(揚聲器)的模擬輸入 SASI APx555: 發(fā)生器: 數(shù)字輸出:750Hz 正弦波,-9dBFS 分析器: 輸入 1:SASI?Tx 的數(shù)字音頻,其中 Fs = 16 KHz、TDM、32 位深度 |

##### PASI higher rate than SASI ADC and DAC SRC Testing with Recording ######

# Target Mode, TDM, 32-bit

# Primary and Secondary ASI, multiple of 48KHz Sampling

# GPIO2=Secondary FSYNC, GPIO1=Secondary BCLK, GPI1=Secondary DIN, GPO1=Secondary DOUT for 4x4

#

w a0 00 00 # Set page 0

w a0 01 01 # Software Reset

w a0 02 09 # Wake up with AVDD > 2v and all VDDIO level

w a0 0a 10 # GPIO1 as input

w a0 0b 10 # GPIO2 as input

w a0 0d 02 # GPI1 as input

w a0 0c 71 # GPO1 as Secondary DOUT

w a0 11 a2 # Enable PASI DIN and Set GPI2A as Secondary FSYNC and GPIO1 as Secondary BCLK

w a0 12 60 # Set GPI1A as Secondary DIN

w a0 18 00 # Enable both Primary and Secondary ASI as independent

w a0 34 40 # PASI BCLK is the input clock source

w a0 19 00 # 1 data input and 1 data output for PASI and SASI

w a0 1a 30 # PASI TDM, 32 bit format

w a0 1e 00 # Tri-state PASI Ch1 to avoid conflict with mix on TDM slot 0

w a0 1f 01 # Tri-state PASI Ch2 to avoid conflict with mix on TDM slot 1

w a0 22 20 # PASI DOUT Ch5 - ASI Loopback data on TDM slot 0

w a0 23 21 # PASI DOUT Ch6 - ASI Loopback data on TDM slot 1

w a0 28 20 # PASI DIN Ch1 on TDM slot 0

w a0 29 21 # PASI DIN Ch2 on TDM slot 1

w a0 00 03 # Set page 3

w a0 1a 30 # SASI TDM, 32 bit format

w a0 1e 20 # SASI DOUT Ch1 on TDM slot 0

w a0 1f 21 # SASI DOUT Ch2 on TDM slot 1

w a0 28 20 # SASI DIN Ch1 on TDM slot 0

w a0 29 21 # SASI DIN Ch2 on TDM slot 1

w a0 00 01 # Set page 1

w a0 17 00 # Default SR-Converter with auto-detect enable

w a0 18 00 # Default auto m:n ratio

w a0 2c d0 # Enable DAC, Side Chain and Loopback Mixer

w a0 00 11 # Set page 0x11

w a0 0c 00 00 40 00 # Route Main DIN Ch1 to LDAC2 Mixer, full scale

w a0 14 40 00 00 00 # Route Main DIN Ch2 to RDAC2 Mixer, full scale

w a0 4c 00 00 40 00 # Route Aux DIN Ch1 to LDAC2 Mixer, full scale

w a0 54 40 00 00 00 # Route Aux DIN Ch2 to RDAC2 Mixer, full scale

w a0 5e 40 00 # ADC Loopback Ch1 to SC_LDAC2 Mixer to mix with LDAC2, full scale

w a0 64 40 00 # ADC Loopback Ch2 to SC_RDAC2 Mixer to mix with RDAC2, full scale

w a0 00 00 # Set page 0

w a0 50 00 # ADC Ch1 diff input, 5KOhm, 2Vrms ac-coupled, audio band

w a0 55 00 # ADC Ch2 diff input, 5KOhm, 2Vrms ac-coupled, audio band

w a0 64 20 # Configure OUT1P/M as differential from DAC1

w a0 65 20 # Configure OUT1P LINEOUT 0dB audio band

w a0 66 20 # Configure OUT1M LINEOUT 0dB 2Vrms Differential

w a0 6b 20 # Configure OUT2P/M as differential from DAC2

w a0 6c 20 # Configure OUT2P LINEOUT 0dB audio band

w a0 6d 20 # Configure OUT2M LINEOUT 0dB 2Vrms Differential

w a0 76 cc # Enable Input and Output Ch1 and Ch2

w a0 78 e0 # Power up ADC, DAC and MICBIAS測試結(jié)果

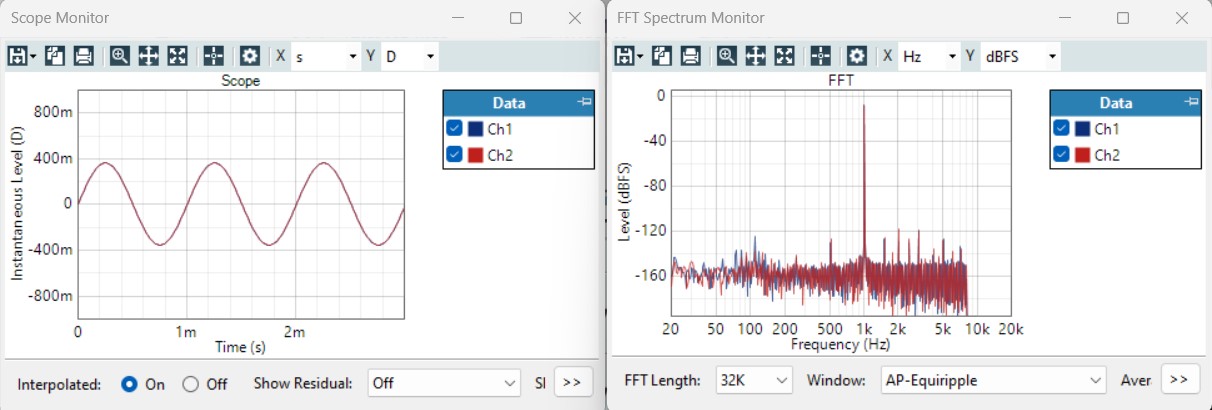

以下各圖顯示了 SRC 之后 SASI TX 處的 ADC 輸出結(jié)果。正如預(yù)期那樣,頻率響應(yīng) (FFT) 在 8KHz(16kHz SASI 速率的 Fs/2)處結(jié)束。

圖 3-7 SRC 之后來自 MIC 輸入的 SASI TX 1KHz 音調(diào):

圖 3-7 SASI ADC 輸出

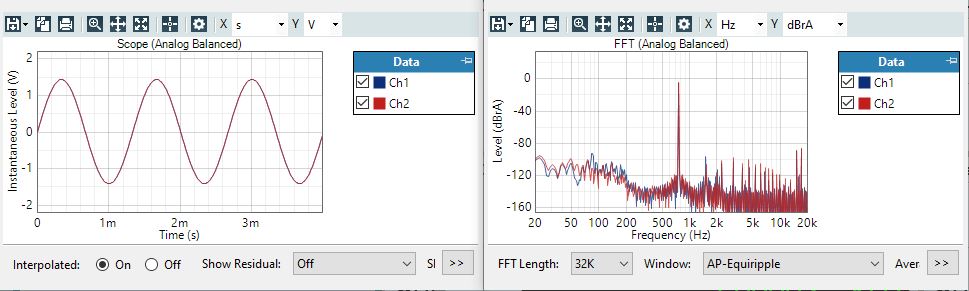

圖 3-7 SASI ADC 輸出在揚聲器輸出端,捕獲的音調(diào)是 SRC 之后 750Hz 的 SASI RX 音調(diào)。PASI RX 音調(diào)將被靜音。PASI TX 是 MIC 輸入與 750Hz SASI RX 音調(diào)的混合信號。

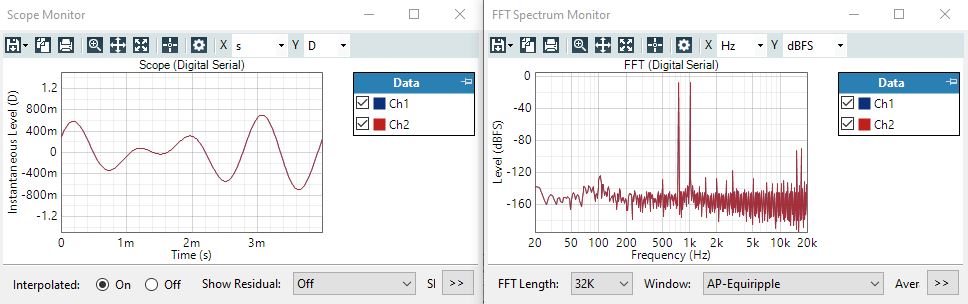

圖 3-8 顯示了 PASI TX 是 MIC 輸入與 SRC 之后 SASI RX 的混合信號。

圖 3-9 顯示了來自 SRC 之后 SASI RX 的 750Hz 音調(diào),其中 PASI 音調(diào)被靜音:

圖 3-8 PASI ADC 輸出

圖 3-8 PASI ADC 輸出 圖 3-9 揚聲器輸出

圖 3-9 揚聲器輸出