ZHCADT8A December 2023 – June 2024 TAA5212 , TAC5111 , TAC5112 , TAC5211 , TAC5212 , TAD5112 , TAD5212

3.1 ADC 采樣速率轉(zhuǎn)換

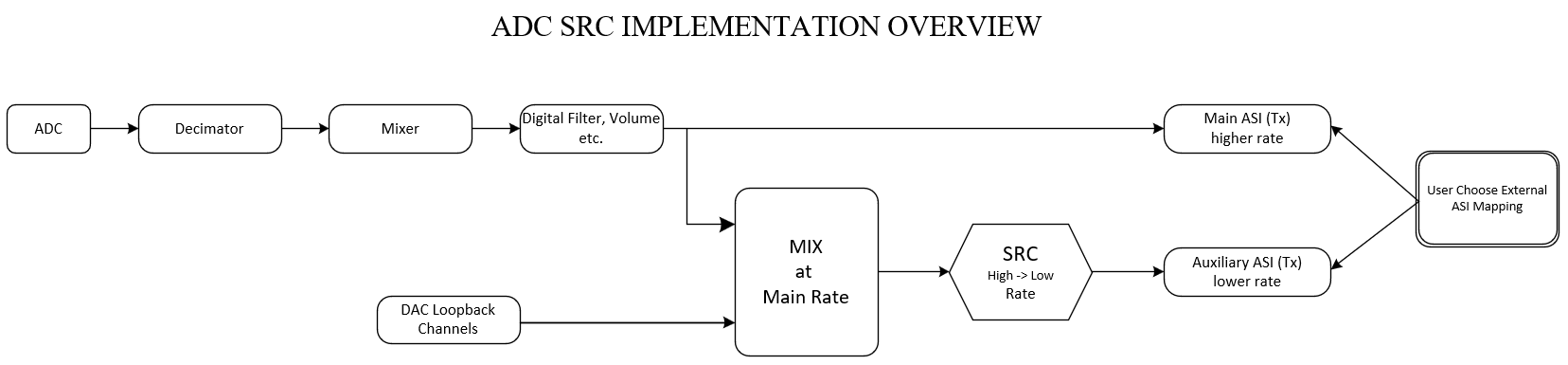

以下方框圖顯示了默認(rèn)模式下的 ADC SRC 流程概述,其中以較高采樣速率(主 Fs)運(yùn)行的 ADC 輸入轉(zhuǎn)換為較低采樣速率(輔助 Fs),并且在另一個(gè) ASI 上可用。用戶可以選擇使用主要 ASI 或次要 ASI 以及較高速率或較低速率的接口。當(dāng)從較低速率選擇主 Fs 時(shí),該流程同樣適用,因此 SRC 將從較低速率轉(zhuǎn)換為較高速率。

SRC 流程可以選擇與 DAC 環(huán)回?cái)?shù)據(jù)進(jìn)行混頻,例如將來(lái)自主機(jī)的音頻數(shù)據(jù)添加到錄制的語(yǔ)音數(shù)據(jù)。

圖 3-1 TAx5x1x ADC SRC 概述 - 默認(rèn)模式

圖 3-1 TAx5x1x ADC SRC 概述 - 默認(rèn)模式用戶可以在混頻時(shí)觀察電平,并設(shè)置系數(shù),以確保輸出不超過(guò)允許的最大值,因?yàn)檩^高的電平會(huì)導(dǎo)致削波或失真。下列公式給出了混頻器輸出電平:

對(duì)于 ADC 混頻器,設(shè)置混頻系數(shù)的公式如下所示,其中 w 表示幅度的權(quán)重或比例。例如,w=0.5 表示幅度的一半,在 32 位 DAC 混頻器系數(shù)中則轉(zhuǎn)換為 'h40000000。一些路徑系數(shù)默認(rèn)為 'h7FFFFFFF,其滿量程幅度為 1。ADC 混頻器系數(shù)通過(guò)寄存器頁(yè)面地址 0x0A 和寄存器地址 0x08 至 0x47 進(jìn)行配置。

對(duì)于數(shù)字環(huán)回(ADC 至 DAC)混頻器,設(shè)置混頻系數(shù)的公式與上述 ADC 混頻器公式相同,并通過(guò)寄存器頁(yè)面地址 0x0A 以及寄存器地址 0x48 至 0x67 進(jìn)行設(shè)置。

對(duì)于 ADC 輔助混頻器,設(shè)置混頻系數(shù)的公式如下所示,其中 w 表示幅度的權(quán)重或比例。該輔助 ADC 混頻器系數(shù)通過(guò)寄存器頁(yè)面地址 0x0B 和寄存器地址 0x30 至 0x37 進(jìn)行配置。

后續(xù)各節(jié)將介紹此 ADC SRC 的一些示例。