ZHCADM8A October 2023 – May 2024 TAA5212 , TAA5242 , TAC5111 , TAC5112 , TAC5142 , TAC5211 , TAC5212 , TAC5242

3.1 差分交流耦合 Power Tune 模式

以下示例提供了在 Power Tune 模式下具有 1.8V AVDD 的差分交流耦合輸入的寄存器設置,用于平衡功耗和性能。B0_P0_R78 (0x4E) 中的寄存器 PWR_TUNE_CFG0 提供了將器件置于功率補償模式的配置。

圖 3-1 Power Tune 模式差分交流耦合寄存器設置

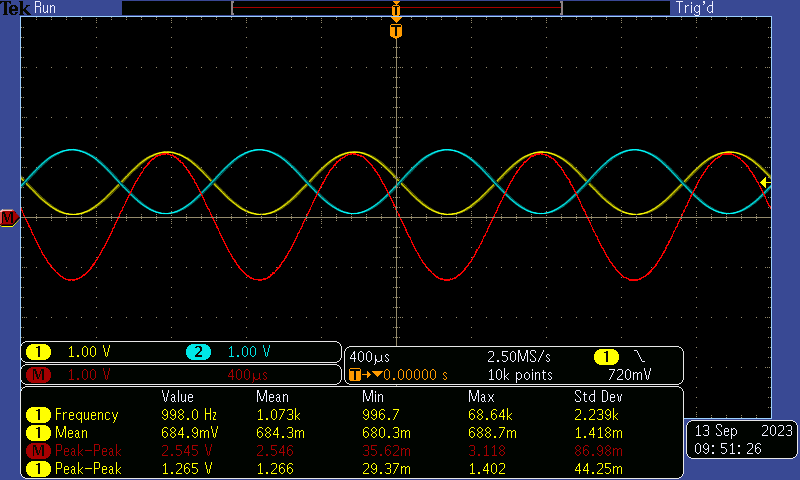

圖 3-1 Power Tune 模式差分交流耦合寄存器設置 圖 3-2 -1dBrG (0dBrG = 1Vrms) 時的 Power Tune 差分交流耦合輸入

圖 3-2 -1dBrG (0dBrG = 1Vrms) 時的 Power Tune 差分交流耦合輸入此處提供了一個頻率圖,描繪了 -60dBrG 輸入時的動態范圍和輸入交流信號短接至地時的 SNR。

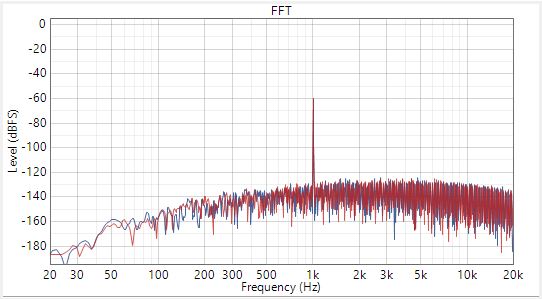

圖 3-3 -60dBrG 時的 Power Tune 模式差分交流耦合動態范圍

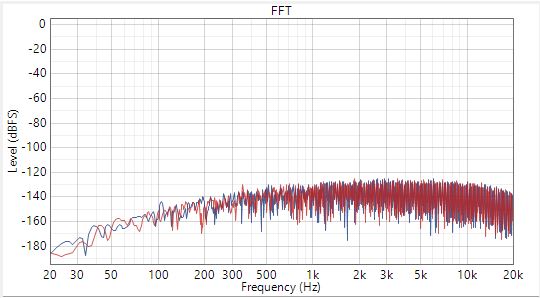

圖 3-3 -60dBrG 時的 Power Tune 模式差分交流耦合動態范圍 圖 3-4 Power Tune 模式差分交流耦合 SNR

圖 3-4 Power Tune 模式差分交流耦合 SNR