ZHCAB56A January 2021 – February 2022 BQ769142 , BQ76942 , BQ76952

7 控制 LD

在高側(cè) FET 設(shè)計(jì)中,LD 引腳通常連接到 PACK+ 并用于 DSG 驅(qū)動(dòng)基準(zhǔn)、喚醒信號(hào)和電流恢復(fù)(如果已選)。數(shù)據(jù)表指出,當(dāng)不使用驅(qū)動(dòng)器時(shí),LD 可能通過(guò)電阻連接到 PACK+ 或者拉至 VSS。如果拉到高電平,它會(huì)阻止器件進(jìn)入關(guān)斷模式。如果連接到 VSS,則不能用于控制電流恢復(fù)。MCU 可使用主機(jī)命令恢復(fù) OCD 事件。該器件提供上拉電阻來(lái)測(cè)試負(fù)載是否移除,因此需要時(shí)可設(shè)計(jì)一個(gè)電路來(lái)控制 LD。如果不通過(guò)命令提供電流恢復(fù),MCU 可以控制電路,或者如果沒有可用的 MCU,可通過(guò) PACK- 引腳電平來(lái)控制它,如圖 7-1 中所示。在發(fā)生使 PACK- 接近 PACK+ 的故障后,PACK 端子上存在負(fù)載時(shí),LD 保持低電平。如果配置適當(dāng),將阻止從電流故障中恢復(fù)。電路在 PACK- 上提供下拉電阻,如果移除負(fù)載,以使此下拉電阻可以關(guān)斷信號(hào) FET Q32,LD 將釋放,BQ769x2 將 LD 拉到高電平,允許電流恢復(fù)。請(qǐng)注意,電路將在 PACK- 上提供下拉電阻,后者通常將 PACK 電壓保持在正常電平附近,當(dāng) PACK 端子上存在負(fù)載時(shí),它會(huì)成為電池上的泄漏點(diǎn)。當(dāng) CHG 保持導(dǎo)通時(shí),柵極驅(qū)動(dòng)電壓將上拉 PACK- 電壓,而根據(jù) R66 和 R67 電阻的值,可能阻止關(guān)斷 Q32。

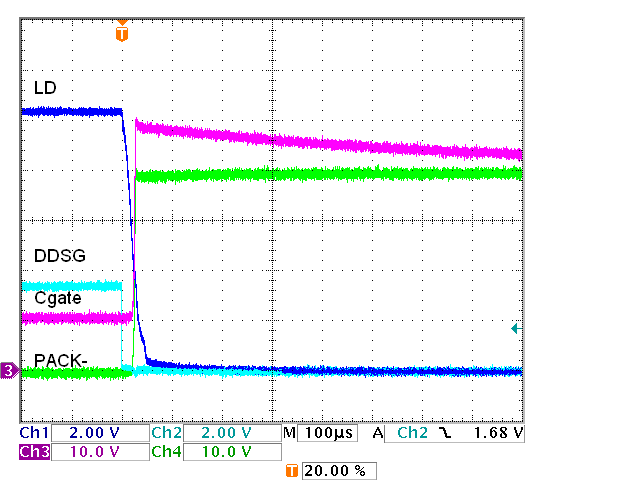

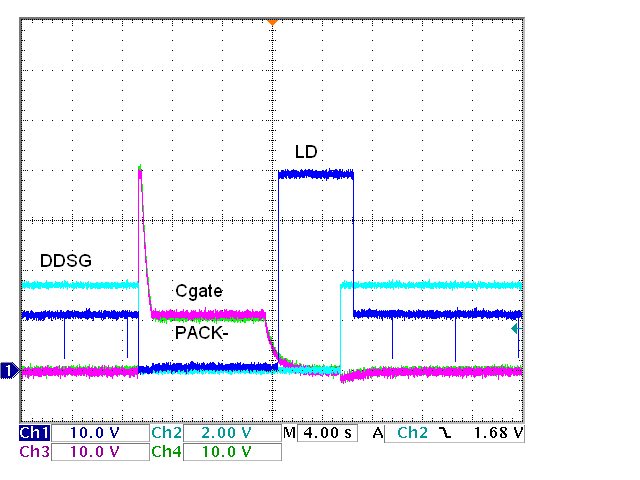

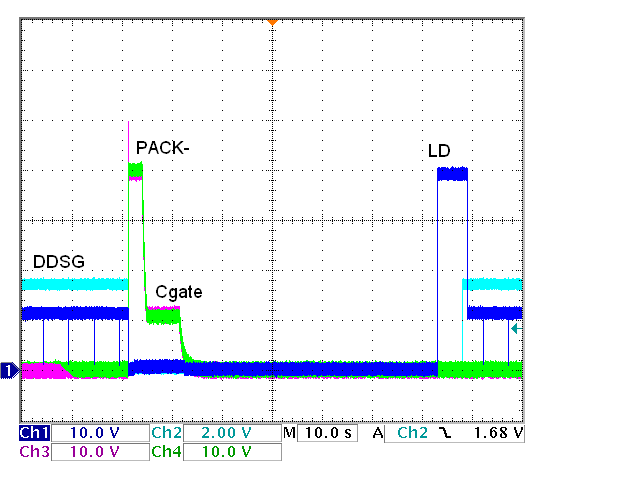

圖 7-2 展示了測(cè)試電路的 OCD 事件。DDSG 關(guān)閉,負(fù)載上拉 PACK-,電路下拉 LD。充電 FET 柵極 Cgate 也會(huì)由 PACK- 上拉,隨著時(shí)間的流逝放電至 PACK- 電平。在 DCHG 導(dǎo)通的情況下,當(dāng)負(fù)載釋放但器件保持喚醒狀態(tài)時(shí),驅(qū)動(dòng)器將 PACK- 向上偏置到驅(qū)動(dòng)器電平附近。根據(jù)為 R66 和 R67 選擇的分壓電阻,電路可能使 LD 保持在低電平,恢復(fù)將不會(huì)發(fā)生,直至連接充電器,如圖 7-3 中所示。BQ769x2 處于睡眠狀態(tài)時(shí),如果 CHG 在睡眠期間關(guān)斷,PACK- 可在負(fù)載移除后下降,恢復(fù)可能快速發(fā)生,如圖 7-4 中所示。如果在 Protections:Load Detect:Active Time 之后并在電流停止后移除負(fù)載,器件將在 Protections:Load Detect:Retry Delay 之后重試,如圖 7-5 中所示。如有必要,器件將一直重試,直至 Protections:Load Detect:Timeout。

圖 7-2 OCD 和受控 LD

圖 7-2 OCD 和受控 LD 圖 7-4 睡眠期間的 OCD 和恢復(fù)

圖 7-4 睡眠期間的 OCD 和恢復(fù) 圖 7-3 OCD 和從充電器連接恢復(fù)

圖 7-3 OCD 和從充電器連接恢復(fù) 圖 7-5 睡眠期間的 OCD 和重試后恢復(fù)

圖 7-5 睡眠期間的 OCD 和重試后恢復(fù)由于低側(cè)開關(guān)和 LD 連接到由上述電路控制的 VSS 或 LD,喚醒信號(hào)需要來(lái)自 TS2。執(zhí)行此操作的簡(jiǎn)單電路如圖 7-6 中所示。當(dāng)朝向 PACK+ 上拉“喚醒”信號(hào)時(shí),TS2 下拉導(dǎo)致 BQ769x2 喚醒。如果喚醒信號(hào)直接連接到 PACK+,電路將在電池上提供持續(xù)漏極。根據(jù)需要調(diào)整 R80 的值并提供瞬態(tài)保護(hù)或使用適合該應(yīng)用的替代電路。