ZHCAB56A January 2021 – February 2022 BQ769142 , BQ76942 , BQ76952

6 晶體管驅動器設計

雖然 IC FET 驅動器功能強大,但有時候用戶不需要集成驅動器的高性能,而可能選擇使用晶體管設計驅動器。電路必須支持功率 FET 柵極的相同電壓范圍。DDSG 和 DCHG 信號的邏輯電平必須轉換為功率 FET 的較高柵極電壓。許多晶體管設計是可行的。如果晶體管驅動器的輸入極性不同,則根據需要調整 BQ769x2 配置中 DDSG 和 DCHG 的極性。圖 6-1 展示了一個測試電路示例。此電路也使用簡單的穩壓器,齊納二極管通向 NPN 發射極跟隨器以實現“12V”驅動器電壓 VFET。R71 和 C68 對 BAT+ 上的瞬態進行濾波,以避免可能耦合 VFET 輸出的情況。VFET 負載通常很小,但選擇 R71 值和額定功率以實現為設計選擇的連續和浪涌電流。雖然電路設計簡單,但在 40V、280uA 下偏置齊納二極管可能導致設計人員的設計更加復雜。放電驅動器使用單一 FET Q36 將電平轉換為 VFET 電壓電平。由于 Q36 反轉信號,它的輸入偏置為高電平,因此當存在 VFET 電壓但未配置 DDSG 信號時,驅動器關斷。DDSG 不得高于絕對最大電壓 6V,因此使用了電壓分壓器。驅動器關斷時,需要 R74 中的偏置電流。Q36 漏極處已轉換電平的信號通過發射極跟隨器 Q34 和 Q37 來驅動 FET 柵極。發射極跟隨器配置將驅動電流通過 FET 開關區,但會限制電壓,避免達到 VFET 和 GND 電平。

對于反向放電驅動器,必須反轉此驅動器的 DDSG 極性。

Settings:Configuration:DCHG Pin Config 0x22

充電驅動器是同相的,也不驅動低電平,因為使用了阻塞二極管。當 DCHG 處于高電平時,Q42 導通 Q41,為充電功率 FET 柵極提供 VFET 電壓。輸出電流受 R102 限制。當 DCHG 處于低電平時,Q42 關斷,R105 關斷 Q41,功率 FET RGS 電阻或額外的柵極電路將功率 FET 柵極拉至低電平。

圖 6-2 展示了由晶體管 FET 驅動器控制的單一放電和充電 FET 電路結構。P 溝道器件 Q2 不附帶 FET,因為它的功能由晶體管驅動器電路 Q41 提供。

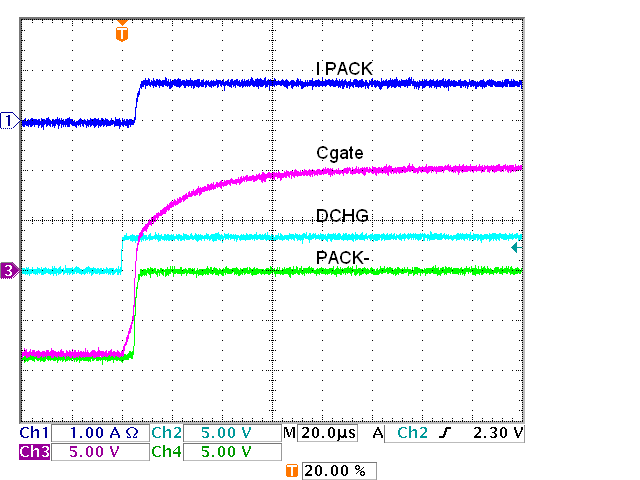

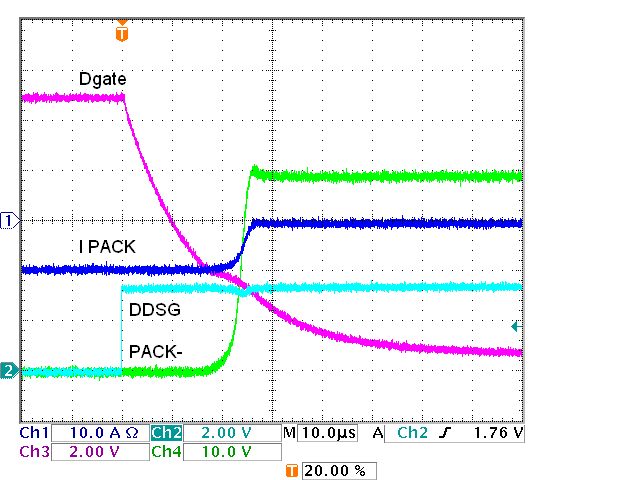

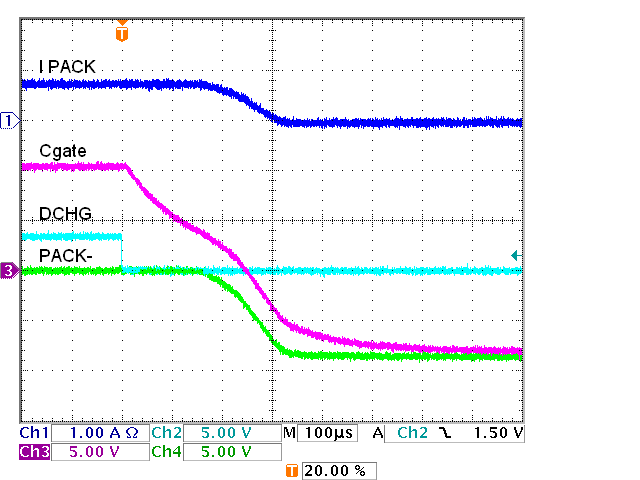

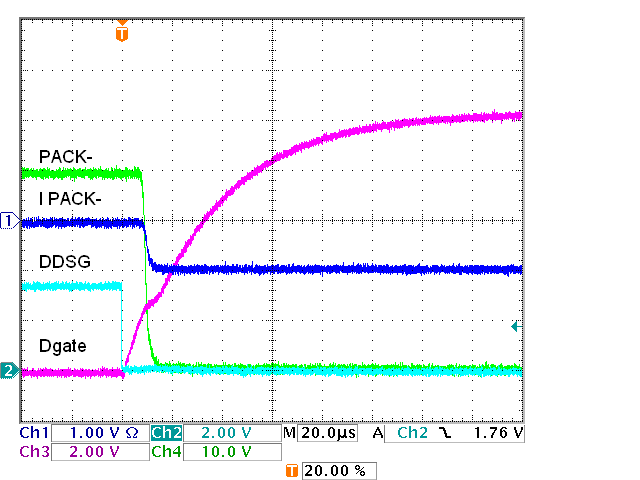

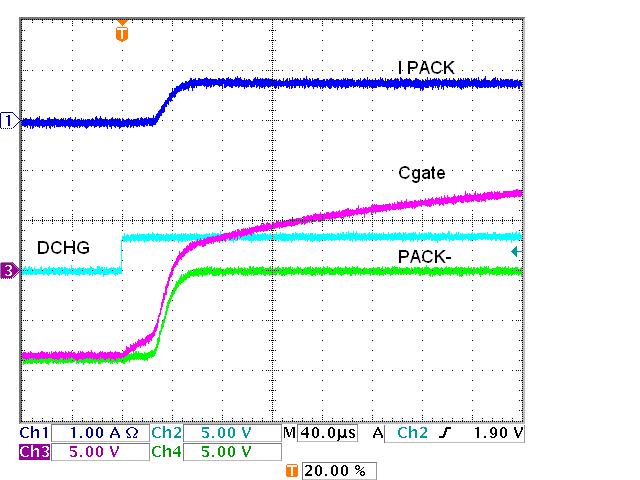

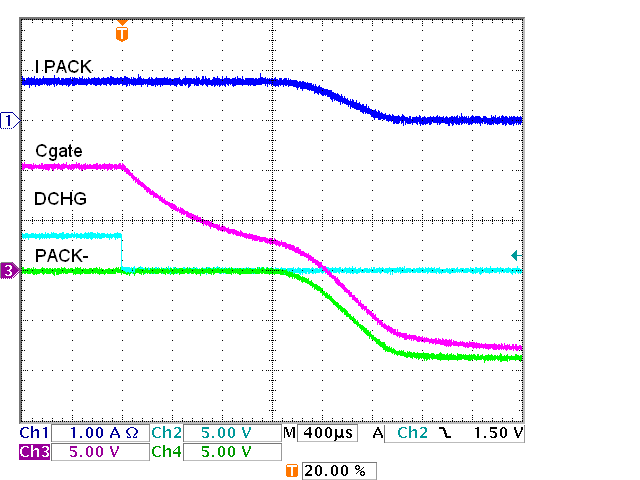

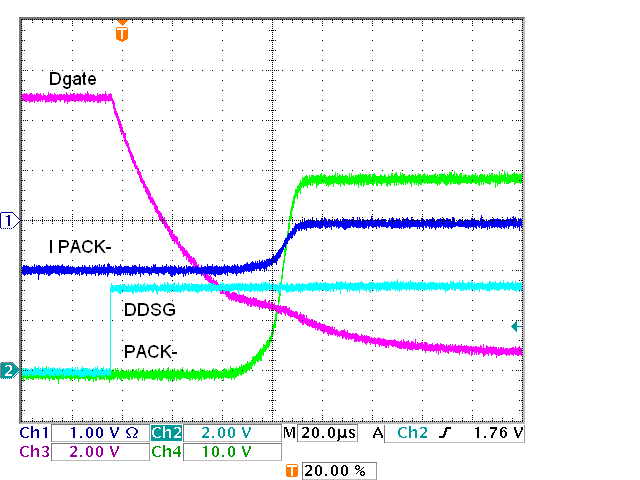

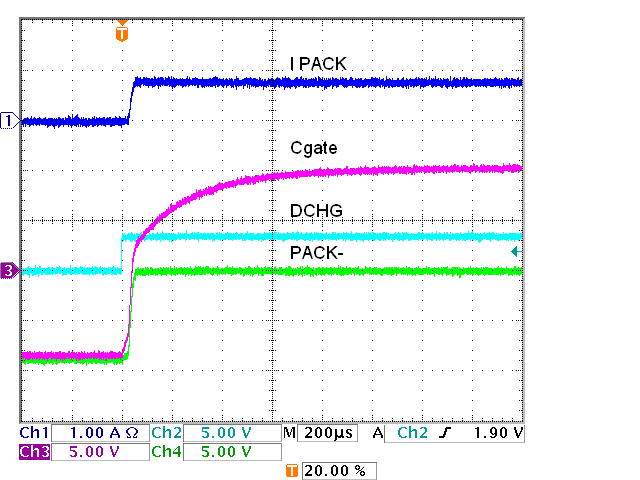

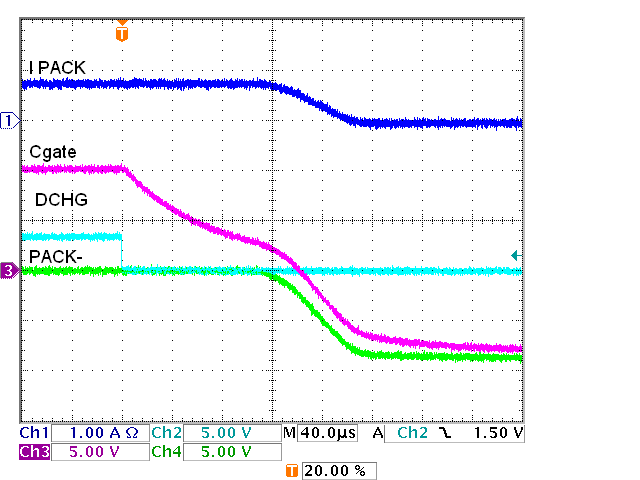

CSD19536KCS FET 用于測試晶體管驅動器電路。圖 6-3 到圖 6-6 展示了開關單一 FET 的結果。放電導通紋波表明,布局可能對于此導通速度敏感,并可能需要較大的 R27 或改進電路。

圖 6-3 晶體管 FET 驅動器驅動一個放電 FET 導通

圖 6-3 晶體管 FET 驅動器驅動一個放電 FET 導通 圖 6-5 晶體管 FET 驅動器驅動一個充電 FET 導通

圖 6-5 晶體管 FET 驅動器驅動一個充電 FET 導通 圖 6-4 晶體管 FET 驅動器驅動一個放電 FET 關斷

圖 6-4 晶體管 FET 驅動器驅動一個放電 FET 關斷 圖 6-6 晶體管 FET 驅動器驅動一個充電 FET 關斷

圖 6-6 晶體管 FET 驅動器驅動一個充電 FET 關斷許多 FET 就像 IC FET 一樣,需要減小柵極驅動器電阻,以提供合適的開關。圖 6-7 展示了一個具有 12 個放電和充電 FET 的測試電路,各 FET 由晶體管驅動器驅動。該電路與 IC FET 驅動器電路非常相似,但晶體管充電驅動器包含一個 P 溝道輸出器件,因此去掉了 Q2。圖 6-8 到圖 6-12 展示了測試結果。圖 6-13 展示了為加快充電關斷,將 R24 降至 91kΩ 后開關速度提高。

圖 6-8 晶體管 FET 驅動器驅動 12 個放電 FET 導通

圖 6-8 晶體管 FET 驅動器驅動 12 個放電 FET 導通 圖 6-10 晶體管 FET 驅動器驅動 12 個充電 FET 導通的細節

圖 6-10 晶體管 FET 驅動器驅動 12 個充電 FET 導通的細節 圖 6-12 晶體管 FET 驅動器驅動 12 個充電 FET 關斷,PNP,1 MΩ

圖 6-12 晶體管 FET 驅動器驅動 12 個充電 FET 關斷,PNP,1 MΩ 圖 6-9 晶體管 FET 驅動器驅動 12 個放電 FET 關斷

圖 6-9 晶體管 FET 驅動器驅動 12 個放電 FET 關斷 圖 6-11 晶體管 FET 驅動器驅動 12 個充電 FET 導通

圖 6-11 晶體管 FET 驅動器驅動 12 個充電 FET 導通 圖 6-13 晶體管 FET 驅動器驅動 12 個充電 FET 關斷,PNP,91 MΩ

圖 6-13 晶體管 FET 驅動器驅動 12 個充電 FET 關斷,PNP,91 MΩ在導通 24 個 FET 期間檢查“12V”VFET 電源,發現導通期間有壓降,如圖 6-14 所示。由于齊納二極管的容差和晶體管 Q33 的基極-發射極壓降,“12V”VFET 電壓的直流電平低于 12V。

圖 6-14 12V 發射極跟隨器,24 個 FET 導通

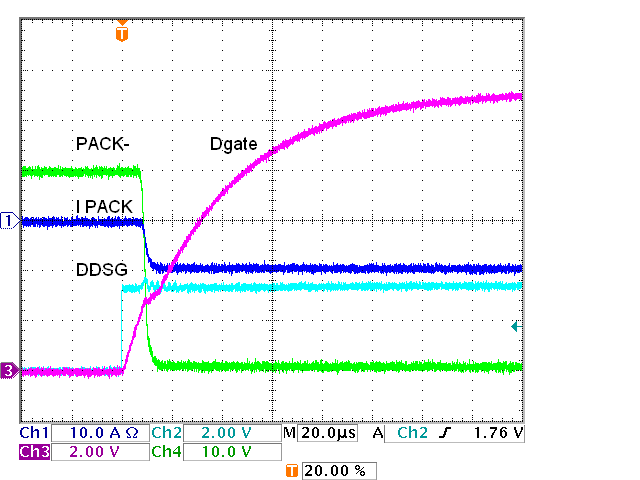

圖 6-14 12V 發射極跟隨器,24 個 FET 導通上述電路有一個 DSG 反向驅動器,始終偏置輸入。發射極跟隨器結構無法驅動到全電壓或 GND。其他拓撲是可行的。圖 6-15 展示了一個使用推挽驅動器的備用放電驅動器。此電路利用 DDSG 極性(導通時為高電平),當驅動器導通時需要偏置電流導通。開關期間沒有擊穿電流。在這種情況下,開關不頻繁,擊穿電流受 R101 限制。開關兩個放電 FET 的示例如圖 6-16 和圖 6-17 所示。

圖 6-16 晶體管 FET 驅動器驅動兩個放電 FET 導通

圖 6-16 晶體管 FET 驅動器驅動兩個放電 FET 導通 圖 6-17 晶體管 FET 驅動器驅動兩個放電 FET 關斷

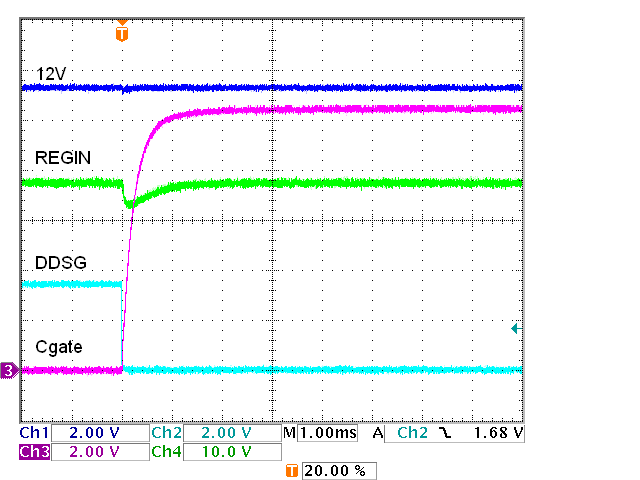

圖 6-17 晶體管 FET 驅動器驅動兩個放電 FET 關斷在濾波輸入 Regin 處可觀察到“12V”VFET 上的驅動器負載。備用驅動器的擊穿電流由電容器提供,在圖 6-18 和圖 6-19 的波形中不明顯。

圖 6-18 12V,推挽驅動器導通

圖 6-18 12V,推挽驅動器導通 圖 6-19 12V,推挽驅動器關斷

圖 6-19 12V,推挽驅動器關斷