SNAU309 October 2025 LMK3H2108

4.2 Performance Data and Results

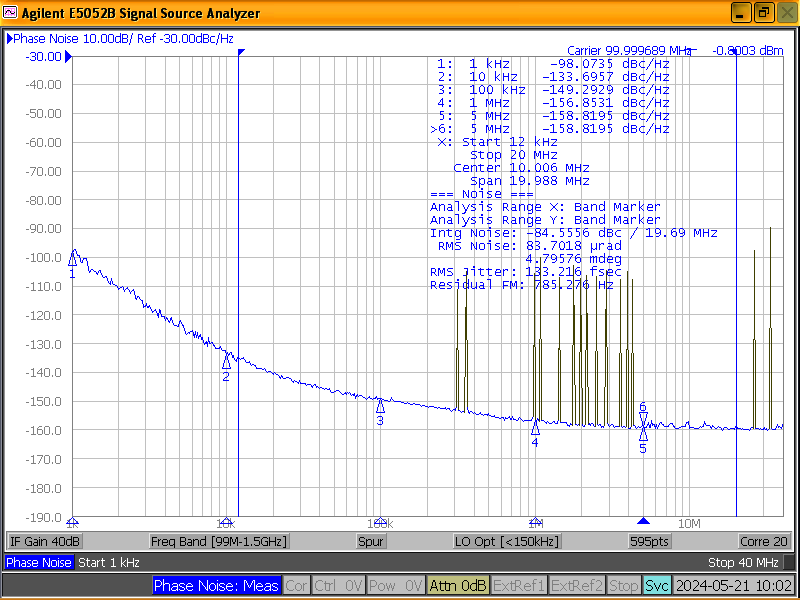

Figure 4-1 LMK3H2108EVM Typical

Performance Using FOD0 Through PATH1, 100MHz

Figure 4-1 LMK3H2108EVM Typical

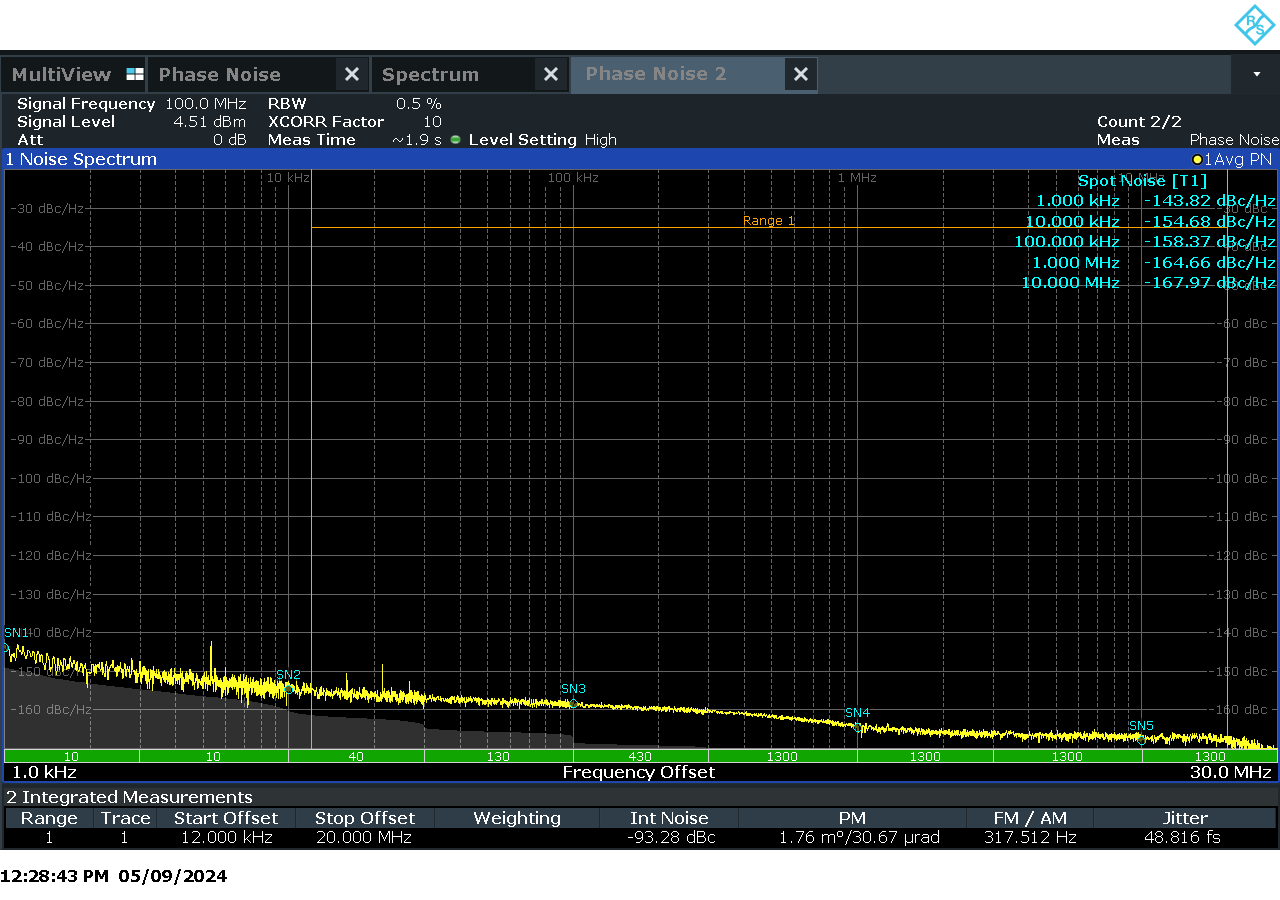

Performance Using FOD0 Through PATH1, 100MHz Figure 4-2 SMA100B 100MHz Input to LMK3H2108EVM for Buffer Mode Measurement

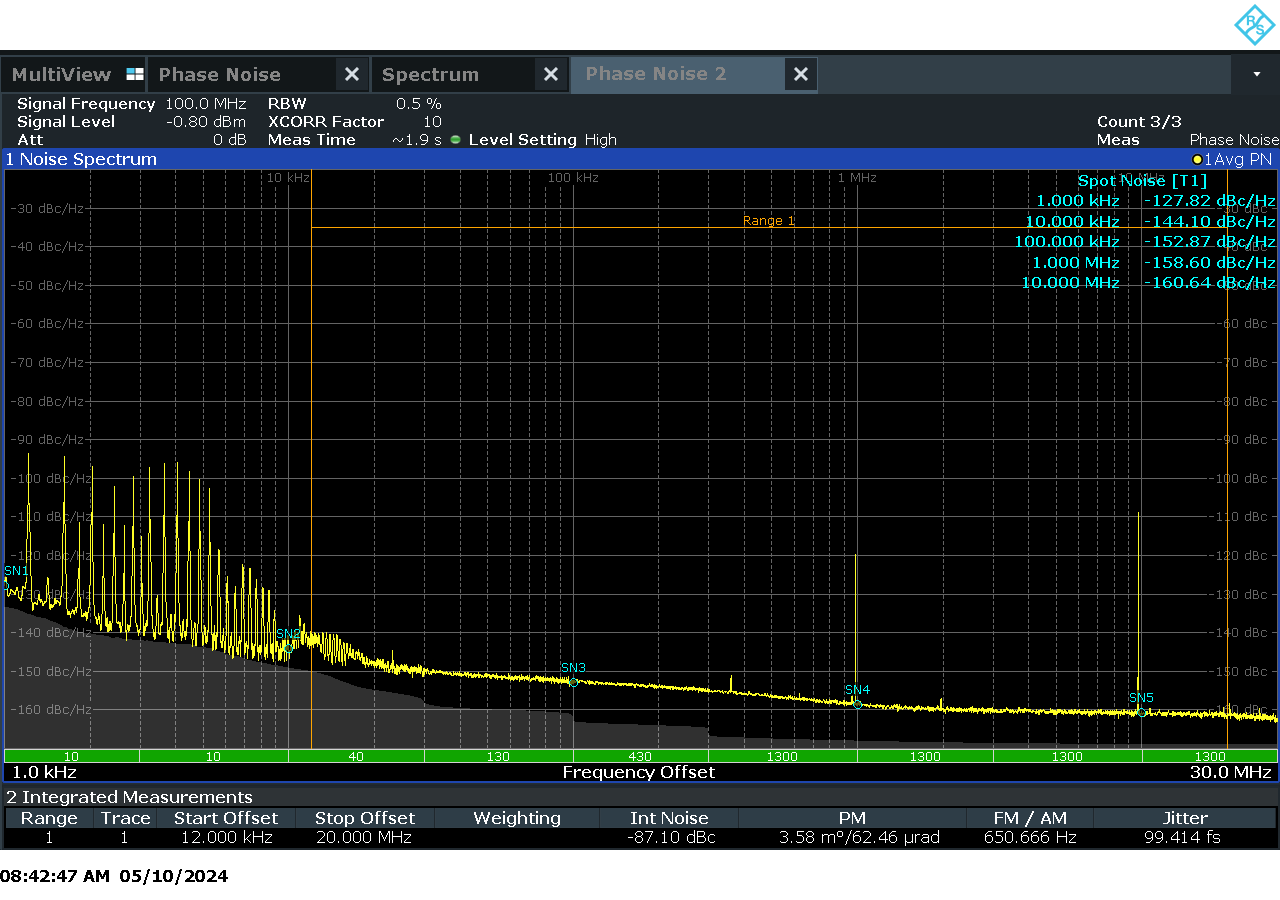

Figure 4-2 SMA100B 100MHz Input to LMK3H2108EVM for Buffer Mode Measurement Figure 4-3 LMK3H2108 Typical Performance in Buffer Mode, SMA100B 100MHz Input

Figure 4-3 LMK3H2108 Typical Performance in Buffer Mode, SMA100B 100MHz InputFigure 4-1 shows the typical performance of the LMK3H2108EVM when all outputs are 100MHz LP-HCSL using FOD0 routed through PATH1. TI has seen a small performance improvement when using PATH1 instead of PATH0 for the clock source, on the order of tens of femtoseconds.

Figure 4-3 shows the performance of the LMK3H2108EVM when used in buffer mode. Figure 4-2 shows the performance of the input provided to the evaluation module for buffer mode testing.