ZHCSMI0F September 2020 – April 2025 DP83TG720S-Q1

PRODUCTION DATA

- 1

- 1 特性

- 2 應(yīng)用

- 3 說明

- 4 引腳配置和功能

- 5 規(guī)格

- 6 詳細(xì)說明

- 7 應(yīng)用和實現(xiàn)

- 8 器件和文檔支持

- 9 修訂歷史記錄

- 10機械、封裝和可訂購信息

封裝選項

機械數(shù)據(jù) (封裝 | 引腳)

- RHA|36

散熱焊盤機械數(shù)據(jù) (封裝 | 引腳)

- RHA|36

訂購信息

7.5.1.1 信號布線

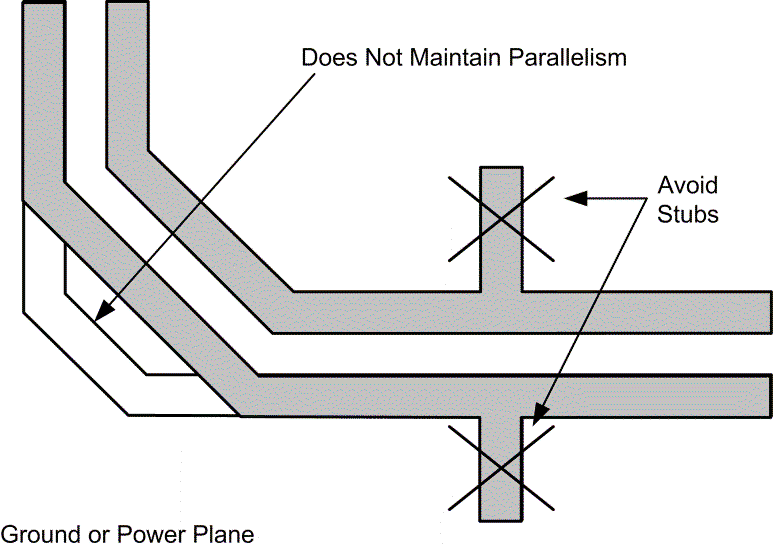

PCB 布線存在損耗,長布線會降低信號質(zhì)量。布線必須盡可能短。除非另有說明,否則所有信號布線必須為 50Ω 單端阻抗。差分布線必須為 50Ω 單端和 100Ω 差分。阻抗不連續(xù)性會產(chǎn)生反射,從而導(dǎo)致發(fā)射和信號完整性問題。對于所有信號布線(特別是差分信號對),必須避免出現(xiàn)殘樁。

圖 7-4 差分信號布線

圖 7-4 差分信號布線在差分對內(nèi),布線必須相互平行,長度匹配。匹配的長度可充分減小延遲差異,避免增加共模噪聲和發(fā)射。長度匹配對 MAC 接口連接也很重要。所有發(fā)送信號布線的長度必須相互匹配,所有接收信號布線的長度也必須相互匹配。

避免信號路徑布線存在交叉或過孔情形。過孔會導(dǎo)致阻抗不連續(xù)情形發(fā)生,應(yīng)盡可能減少過孔情形。在同一層布線差分信號對。不同層的信號之間至少要有一個返回路徑平面,避免存在交叉情形。差分對之間必須始終保持恒定的耦合距離。為提高便利性和效率,TI 建議首先布線關(guān)鍵信號(即 MDI 差分對、基準(zhǔn)時鐘和 MAC IF 布線)。