ZHCUA92E May 2022 – May 2025

- 1

- 說明

- 特性

- 4

- 1前言:使用前必讀

- 2套件概述

- 3電路板設置

- 4硬件說明

- 5EVM 修訂版本設計更改

- 6硬件設計文件

- 7參考文獻

- 商標

- 8修訂歷史記錄

4.3 復位

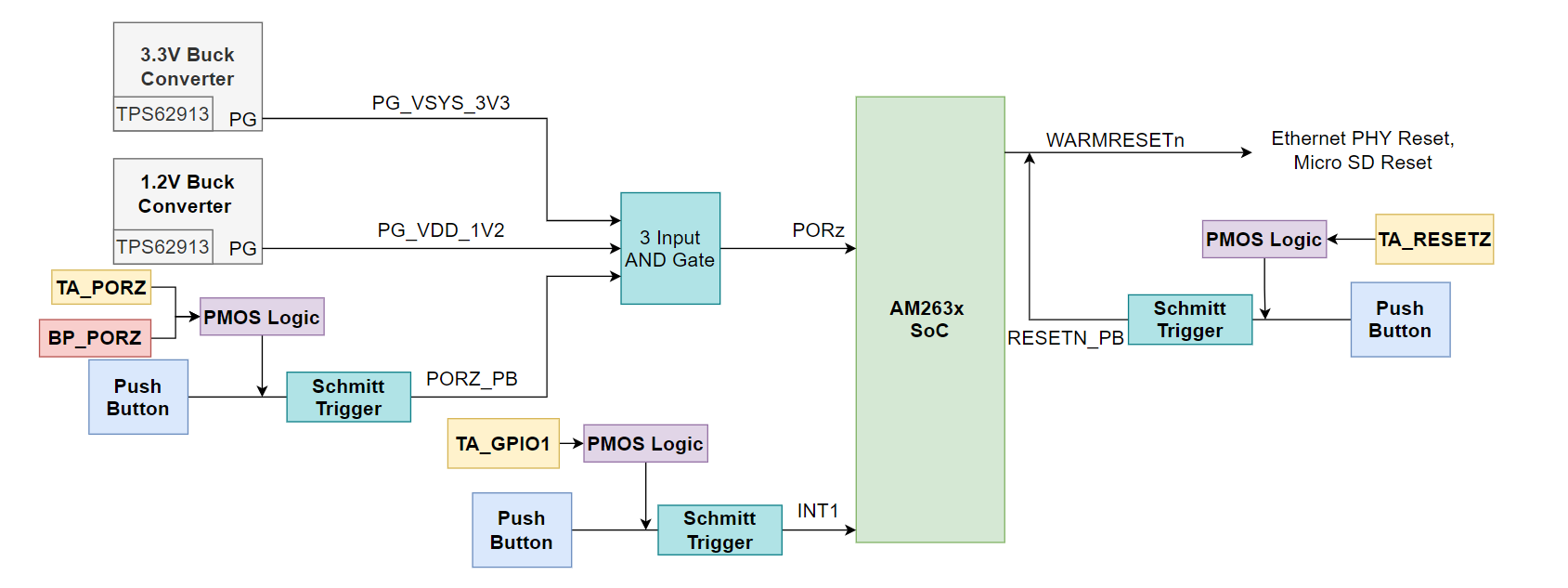

圖 4-2 展示了 AM263x LaunchPad 的復位架構

圖 4-2 復位架構

圖 4-2 復位架構AM263x LaunchPad 具有以下復位:

- PORz 為上電復位

- WARMRESETn 為熱復位

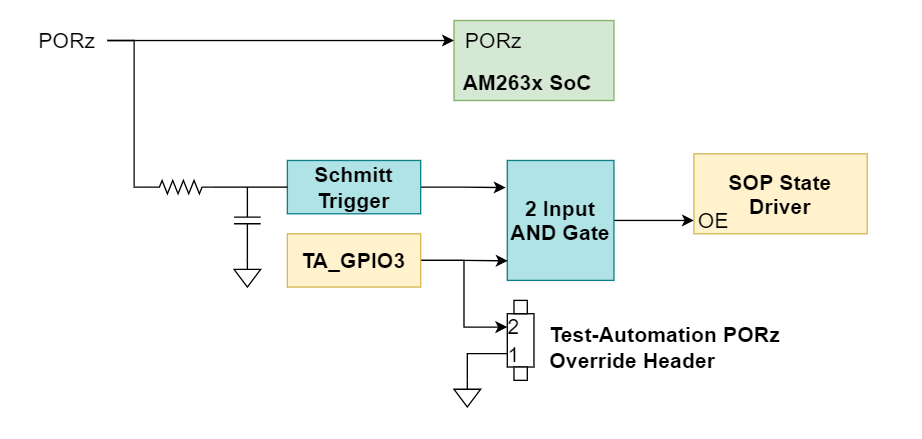

圖 4-3 PORz 復位信號樹

圖 4-3 PORz 復位信號樹PORz 信號由 3 路輸入與門驅動,后者會在以下情況下生成主域上電復位:

- 3.3V 降壓轉換器 (TPS62913) 電源正常輸出因輸出電壓低于電源正常閾值而被驅動為低電平時。

- 1.2V 降壓轉換器 (TPS62912) 電源正常輸出因輸出電壓低于電源正常閾值而被驅動為低電平時。

- 按下用戶按鈕 (SW2) 時。

- P 溝道 MOSFET 柵極的信號為邏輯低電平,這會導致 PMOS 的 V_GS 小于零,因此 PORz 信號會連接到 PMOS 漏極,而后者會直接連接到地。可為 PMOS 柵極生成邏輯低電平輸入的信號包括:

- 來自測試自動化接頭的 TA_PORZ 輸出

- 來自任一 BoosterPack 站點的 BP_PORZ 輸出。

PORz 信號連接到:

- AM263x SoC PORz 輸入

- BOOTMODE 狀態驅動器的輸出使能輸入

- RC 濾波器在 GND 與 3.0V 電源之間產生 1ms 的延遲,以便 SOP 狀態驅動器的輸出使能輸入保持低電平的時間超過 PORz 取消置位后所需的 SOP 保持時間。

借助測試自動化 PORz 覆蓋接頭,可在安裝了跳線的情況下將 TA_GPIO3 保持為低電平。因而能夠從測試自動化接口進行引導模式控制。

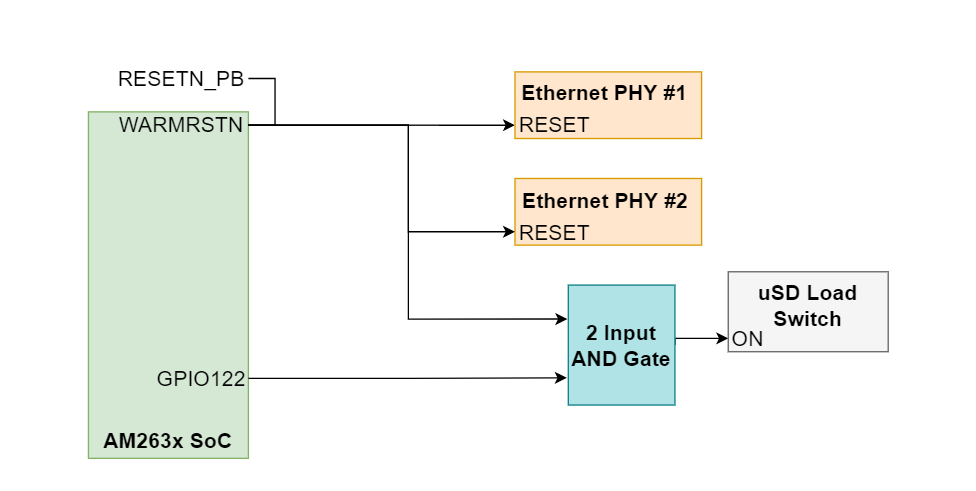

圖 4-4 WARMRESETn 復位信號樹

圖 4-4 WARMRESETn 復位信號樹WARMRESETn 信號會在以下情況下生成主域熱復位:

- 按下用戶按鈕 (SW3) 時。

- 測試自動化接頭輸出邏輯低電平信號 (TA_RESETz)到 P 溝道 MOSFET 柵極,導致 PMOS 的 V_GS 小于零,因此 RESETz 信號會連接到直接與接地連接的 PMOS 漏極。

WARMRESETn 信號連接到:

- AM263x SoC WARMRESETN 輸出

- 按下按鈕+ PMOS 邏輯生成的 RESETN_PB 信號

- 通過 2 路輸入與門的 Micro SD 負載開關控制輸入以及 AM263x SoC 驅動 GPIO 信號 (GPIO122)

- 兩個以太網 PHY 的復位輸入

AM263x LaunchPad 還具有 SoC 的外部中斷 INT1,以下情況下會發生該中斷:

- 按下用戶按鈕 (SW4) 時。

- 測試自動化接頭輸出邏輯低電平信號 (TA_GPIO1)到 P 溝道 MOSFET 柵極,導致 PMOS 的 V_GS 小于零,因此 INTn 信號會連接到直接與接地連接的 PMOS 漏極。