ZHCABE6A September 2021 – April 2022 PCM3120-Q1 , PCM5120-Q1 , PCM6120-Q1 , TLV320ADC3120 , TLV320ADC5120 , TLV320ADC6120

2 自動增益控制

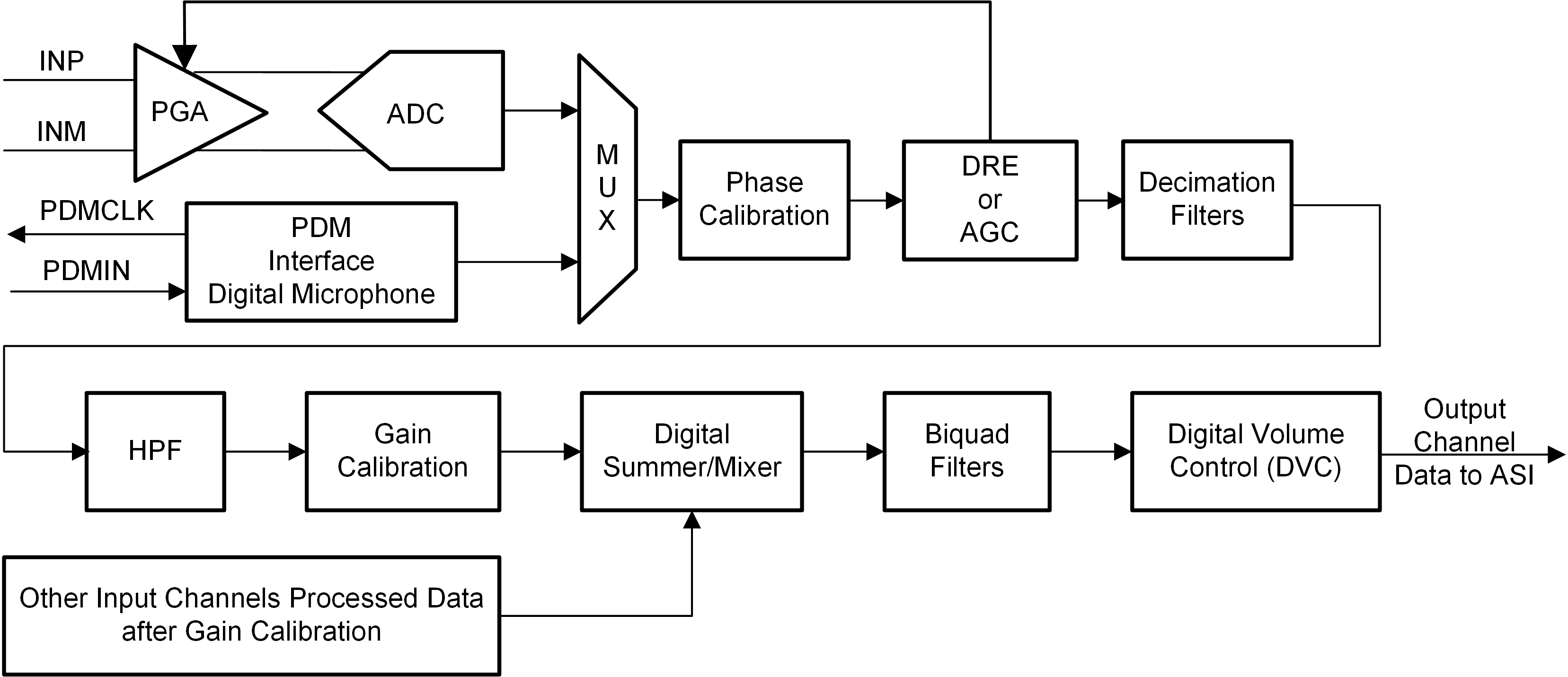

AGC 算法是一種混合信號解決方案,其中通道的模擬可編程增益放大器 (PGA) 由閉環控制數字算法控制。圖 2-1 顯示了器件的信號處理鏈。

圖 2-1 AGC 方框圖

圖 2-1 AGC 方框圖為了響應輸入信號的變化,AGC 算法監測來自 ADC 的數字化信號并調整 PGA 以保持恒定的目標電平。如果信號低于目標電平,則 AGC 會增大 PGA 增益。如果信號高于目標電平,則 AGC 會減小 PGA 增益。使用 PGA 的模擬電路來改變輸入信號以提供最佳的噪聲性能,因為該電路避免了數字電路中增加量化噪聲的增益調整。此外,AGC 算法在 PGA 更改期間使用小階躍幅度來減少輸入信號中的失真。

TLV320ADCx120 和 PCMx120-Q1 系列最多支持兩個模擬外部輸入通道,而所有輸入通道都支持 AGC。這些器件支持來自模擬麥克風源或輔助線路輸入的差分或單端信號。模擬麥克風輸入支持駐極體電容器和微機電 (MEMS) 麥克風。盡管這些器件還支持數字脈沖密度調制 (PDM) 數字麥克風,但由于數字麥克風的模擬增益無法控制,AGC 不支持數字通道。

TLV320ADC5120、TLV320ADC6120、PCM5120-Q1 和 PCM6120-Q1 還支持模擬通道上的動態范圍增強器 (DRE) 算法以擴大動態范圍。DRE 算法控制 PGA 以降低低電平信號的本底噪聲。無法同時使用 DRE 和 AGC 算法,因為這兩種算法都控制 PGA。如表 2-1 所示,可以使用 DSP_CFG1 寄存器(頁面 = 0x00,地址 = 0x6C)的 DRE_AGC_SEL 位來選擇 DRE 或 AGC。可以使用 CH1_DREEN (P0_R60_D0)、CH2_DREEN (P0_R65_D0)、CH3_DREEN (P0_R70_D0) 和 CH4_DREEN (P0_R75_D0) 寄存器位為每個通道獨立啟用或禁用 AGC 或 DRE。

| 位 | 字段 | 類型 | 復位 | 說明 |

|---|---|---|---|---|

| 3 | DRE_AGC_SEL | R/W | 0h | 為任何通道選擇 DRE 或 AGC(如果啟用)。 0d = 選擇 DRE。 1d = 選擇 AGC。 |