ZHCSUP2 March 2025 BQ76907-Q1

PRODUCTION DATA

- 1

- 1 特性

- 2 應用

- 3 說明

- 4 器件比較表

- 5 引腳配置和功能

-

6 規格

- 6.1 絕對最大額定值

- 6.2 ESD 等級

- 6.3 建議運行條件

- 6.4 BQ76907-Q1 熱性能信息

- 6.5 電源電流

- 6.6 數字 I/O

- 6.7 REGOUT LDO

- 6.8 電壓基準

- 6.9 庫侖計

- 6.10 庫侖計數字濾波器

- 6.11 電流喚醒檢測器

- 6.12 模數轉換器

- 6.13 電芯電壓測量精度

- 6.14 電芯均衡

- 6.15 內部溫度傳感器

- 6.16 熱敏電阻測量

- 6.17 硬件過熱檢測器

- 6.18 內部振蕩器

- 6.19 充電和放電 FET 驅動器

- 6.20 基于比較器的保護子系統

- 6.21 時序要求 - I2C 接口,100kHz 模式

- 6.22 時序要求 - I2C 接口,400kHz 模式

- 6.23 時序圖

- 6.24 典型特性

- 7 詳細說明

- 8 應用和實施

- 9 器件和文檔支持

- 10修訂歷史記錄

- 11機械、封裝和可訂購信息

8.2.6 FET 驅動器關斷

當低側 CHG 和 DSG FET 驅動器被觸發而關閉其各自的 FET 時,它們的工作方式有所不同。DSG 驅動器包含一個內部開關,當驅動器被禁用時,該開關會將 DSG 引腳驅動至 VSS 引腳電平。該驅動器指定為在具有 20nF 容性負載且 DSG 引腳和 DSG 柵極之間具有 100Ω 串聯電阻時下降時間最大。如果將驅動器與較大的容性負載一起使用,下降時間通常會增加。系統設計人員可以根據使用的電路板組件和 DSG FET 來優化串聯電阻值。

DSG 引腳和 DSG FET 柵極之間的外部串聯柵極電阻用于調整關斷瞬態的速度。低電阻(如 100Ω)可在短路事件期間提供快速關斷,但這可能會在 FET 禁用時導致 電池組頂部的電感尖峰過大。較大的電阻值(例如 1kΩ 或 4.7kΩ)會降低 此速度和相應的電感尖峰水平。

CHG FET 驅動器會將 CHG 引腳放電至 VSS 引腳電平,但它包括一個額外的串聯 PFET 以支持低于 VSS 的電壓。當電池包深度放電時,通常需要這樣做,例如,如果 7 節串聯電池包中每節電芯的電壓為 2.5V,則相對于 器件 VSS,PACK+ = 17.5V。然后,如果在 CHG FET 被禁用時連接了充電器,并相對于 PACK– 在 PACK+ 上施加完全充電電壓,例如每節電池 4.3V 或 7 節電池包 30.1V,這會導致 PACK– 相對于 VSS 降至大約 –12.6V。要使 CHG FET 保持禁用狀態,其柵極電壓必須降至接近此 –12.6V 電平。

為了支持這種情況,BQ76907-Q1 中的 CHG FET 驅動器設計為通過在該引腳上包含一個串聯 PFET 且其柵極連接到 VSS,能夠承受相對于 VSS 引腳電壓低至 –25V(推薦)的電壓。當 CHG 驅動器被禁用時,該驅動器會將引腳電壓拉低。當引腳電壓接近 VSS 時,PFET 被禁用,從而使該引腳變為高阻抗。此時,CHG FET 上的外部柵源電阻器會將引腳電壓拉低至 PACK– 電平,使 CHG FET 保持禁用狀態。

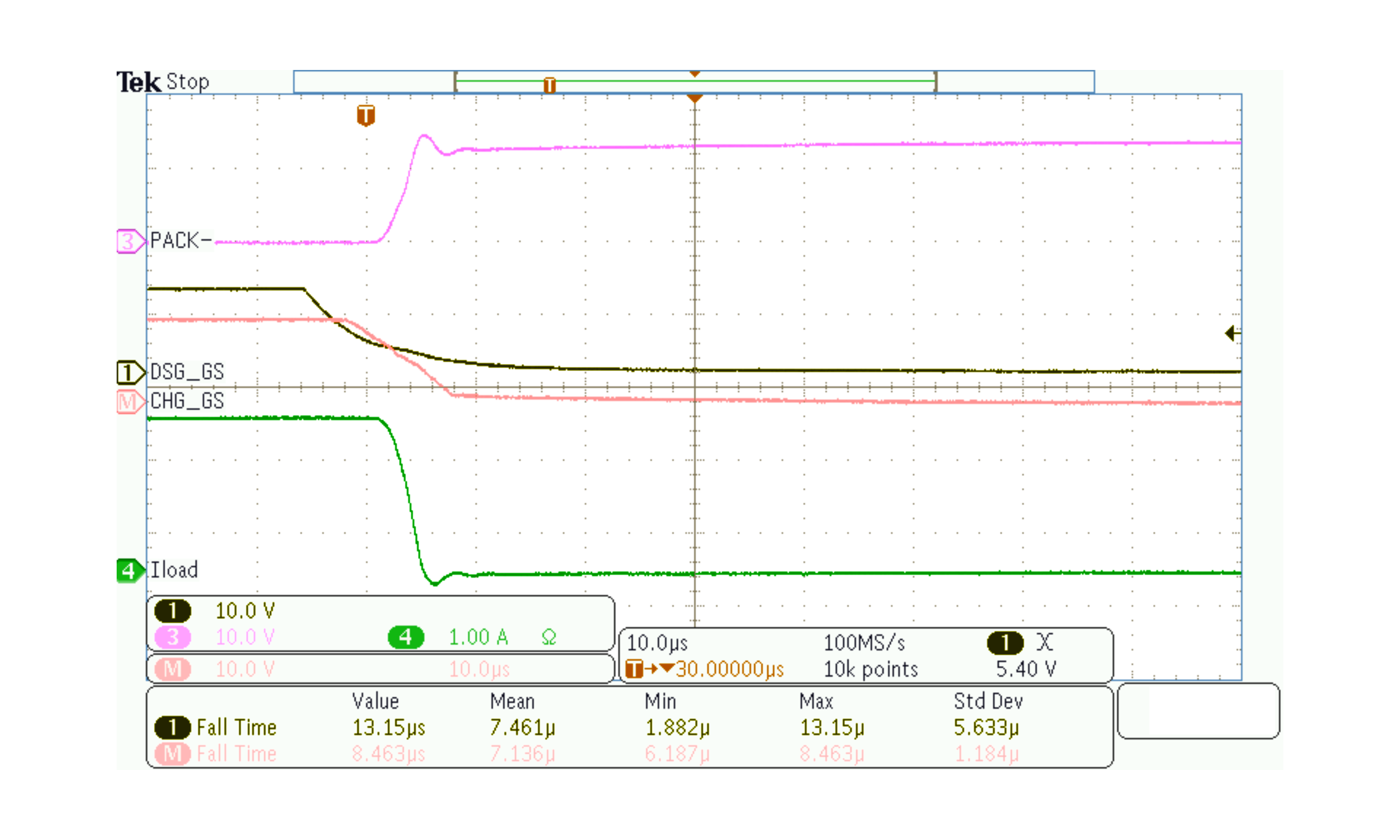

下面顯示了 CHG 和 DSG 驅動器關斷情況下示波器捕獲的波形,其中相應引腳驅動 CSD18532Q5B NFET 柵極,其典型 Ciss 為 3900pF。圖 8-6 顯示了在 DSG 引腳和 FET 柵極之間使用 1.35kΩ 串聯柵極電阻器以及在 PACK+ 和 PACK– 之間連接 2A 負載時的信號。

圖 8-6 中速 FET 關斷,使用一個 1.35kΩ 串聯柵極電阻器,并且 PACK+ 和 PACK– 之間具有 2A 負載。

圖 8-6 中速 FET 關斷,使用一個 1.35kΩ 串聯柵極電阻器,并且 PACK+ 和 PACK– 之間具有 2A 負載。圖 8-7 顯示了一個較慢的關斷情況,其中使用一個 4.5kΩ 串聯柵極電阻器且 PACK+和 PACK– 之間具有 2A 負載。

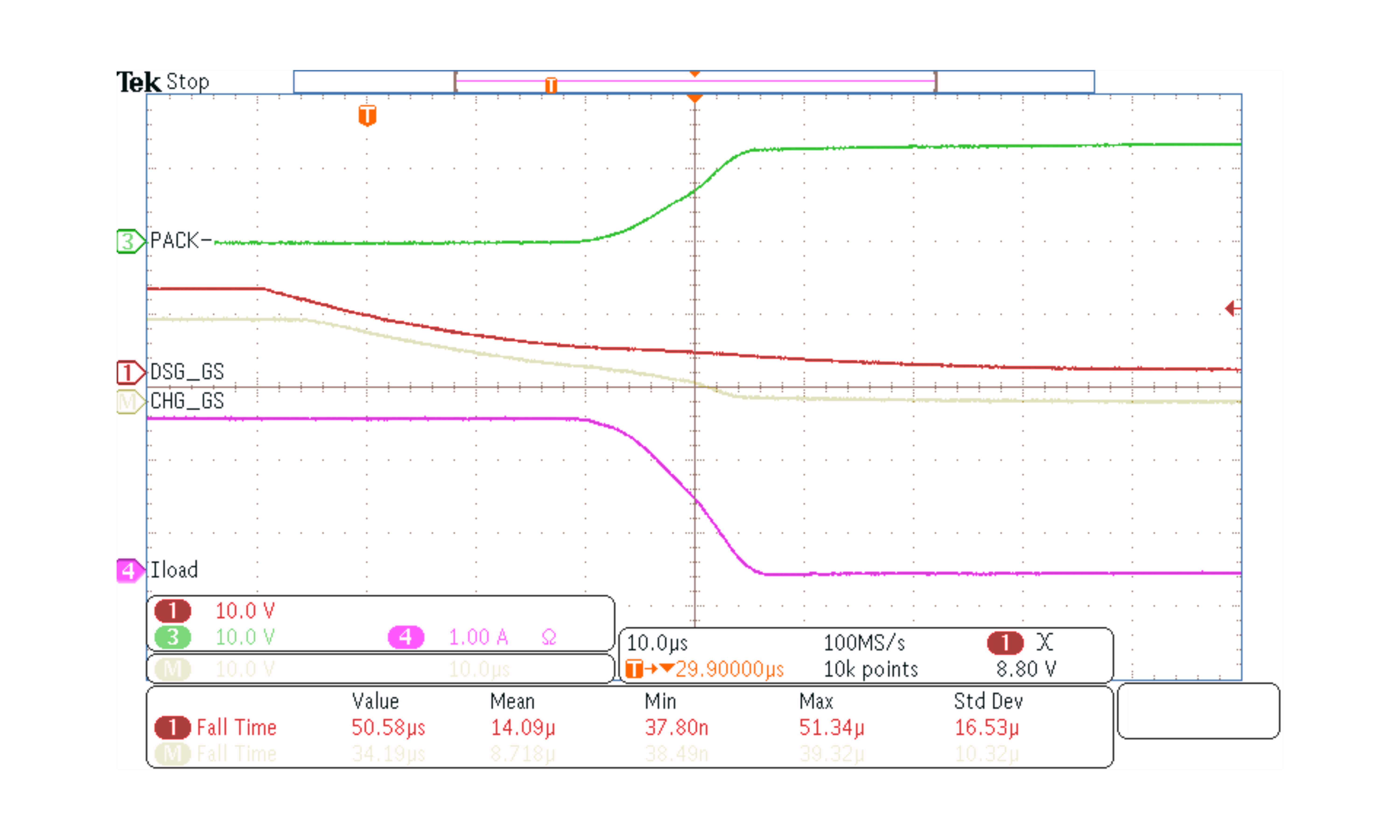

圖 8-7 使用 4.5kΩ 串聯柵極電阻器時的較慢關斷情況

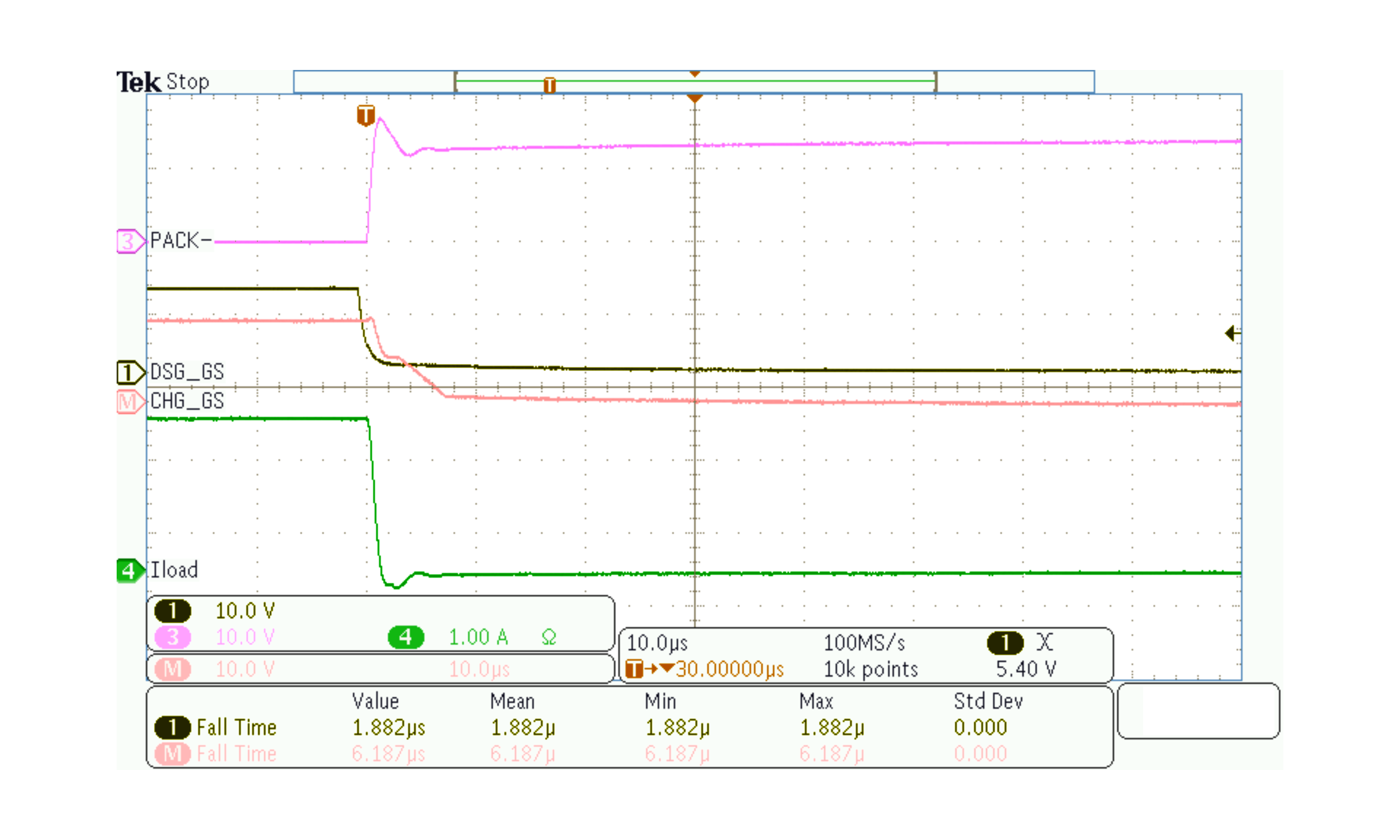

圖 8-7 使用 4.5kΩ 串聯柵極電阻器時的較慢關斷情況圖 8-8 顯示了快速關斷情況,其中在 DSG 引腳和 FET 柵極之間使用了一個 100Ω 串聯柵極電阻器。

圖 8-8 使用 100Ω 串聯柵極電阻器時的快速關斷情況

圖 8-8 使用 100Ω 串聯柵極電阻器時的快速關斷情況