ZHCAFB9 May 2025 TPS628301 , TPS628302 , TPS628303 , TPS628304

使用 TPS62830x 為 LPCAMM2 供電

簡介

LPCAMM2 內存模塊需要多個電壓軌,例如 1.8V (VDD1)、1.05V (VDD2H)、0.9V (VDD2L) 和 0.5V/0.3V (VDDQ),它們均由 JESD318(壓縮附加內存模塊 (CAMM2) 通用標準中的 JDEC 標準)進行了標準化。JESD301-3(適用于 LPDDR5 的 PMIC5200 電源管理 IC 規范)涵蓋了這些電壓軌。但是在 LPCAMM2 標準 (JESD318A) 中也敘述了一種替代架構。這種替代架構使用用于 DDR5 存儲器的 PMIC5100 電源管理 IC 來生成 VDD1 和 VDD2 電壓軌,并將其與用于生成 VDDQ 的單獨離散穩壓器相結合,如圖 1中所示。

圖 1 LP5 CAMM2 VDDQ 常見電力輸送方法中的 TPS62830x

圖 1 LP5 CAMM2 VDDQ 常見電力輸送方法中的 TPS62830x本應用簡報介紹了一種利用 TPS62830x 器件系列應對離散 VDDQ 設計挑戰的方法。

使用 TPS62830x 的離散 VDDQ 電源軌

根據 LPCAMM2 中 VDDQ 電壓軌的要求,TPS62830x 系列本身支持 0.5V 的輸出電壓。通常,所需的 VDDQ 電流消耗在1A 至 3A 范圍內,具體取決于存儲器大小和 VDDQ 分離軌方法或通用方法的實現情況。TPS62830x 系列包含 1、2、3 和 4A 器件型號,并具備類似的性能。特別是,高輸出電壓精度和優化的負載瞬態性能可以滿足 VDDQ 要求的特性。根據器件特定數據表,建議將瞬態優化型 BOM 以及一個 0.24μH 電感器和 2 個 22μF 輸出電容器用于該 VDDQ 電源應用中。0.5V 的輸出電壓不需要反饋分壓器,因為這是原生 FB 基準電壓。可將 MODE 引腳設置為高電平以啟用強制 PWM 操作。圖 2展示了 LPCAMM2 上的 VDDQ 示例應用。

圖 2 采用 TPS62830x 的 LPCAMM2 VDDQ 的示例應用

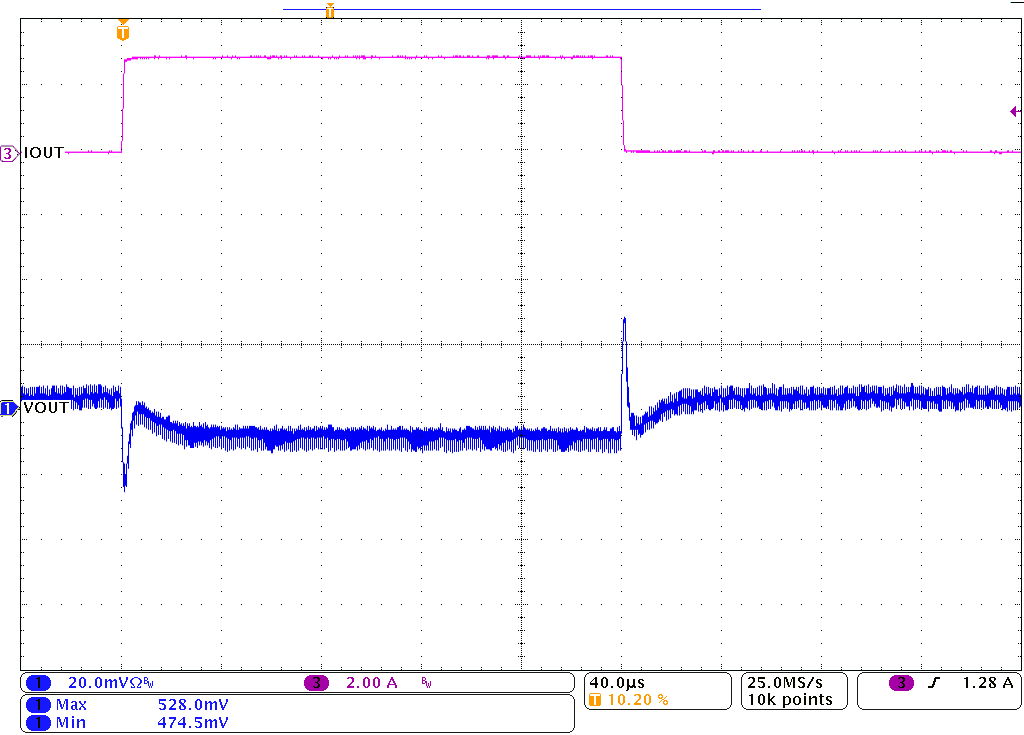

圖 2 采用 TPS62830x 的 LPCAMM2 VDDQ 的示例應用圖 3展示了在該配置中當 2.5A/μs 時針對負載階躍為 0.1A 至 3A 的負載瞬態性能。

圖 3 在 2.5A/μS 時,TPS628303 負載瞬態響應為 0.1A 至 3A

圖 3 在 2.5A/μS 時,TPS628303 負載瞬態響應為 0.1A 至 3A所示的負載瞬態包括靜態負載調節和開關噪聲引起的電壓紋波。輸出電壓不超過 JESD209-5C(低功耗雙倍數據速率 LPDDR 5/5X)中規定的 0.47V 至 0.57 的電壓范圍。

TPS62830x 以通常為 300μs 的固定軟啟動時間斜升。加上大約 120μs 的啟用延遲時間,輸出電壓在 420μs(最大 660μs)內完全供電,如圖 4所示。

圖 4 TPS628303 在1A 負載下軟啟動

圖 4 TPS628303 在1A 負載下軟啟動根據 JESD209-5C,VDDQ 電源軌應斜升為所有電源序列中的最后一個。為 TPS62830x 指定的快速啟動時間能滿足所需的最大總功率斜升持續時間 20ms。

JESD209-5C 中定義的斷電序列需要 VDDQ 以所有電源軌中最快的速度下降。在不受控制的斷電情況下,最大斷電斜降時間指定為 2s。TPS62830x 具有強大的 400mA 有源放電電流,能進行快速斜降,即使在 0A 負載下也是如此,如圖 5所示。

圖 5 TPS628303 在 0A 負載下禁用

圖 5 TPS628303 在 0A 負載下禁用通過 TPS62830x 實現 DVFSQ 支持

盡管 JESD318(壓縮連接的內存模塊 (CAMM2) 通用標準)在離散 VDDQ 實現中明確排除了對 DVFSQ 提供 0.3V 的支持,但可以使用圖 6中的電路模擬 DVFSQ 控制。

圖 6 TPS62830x DVFSQ 實現示例

圖 6 TPS62830x DVFSQ 實現示例開關斷開時的輸出電壓可以通過方程式 1計算得出。

開關閉合時的輸出電壓可以通過方程式 2計算得出。

圖 6中的電阻值針對斷開的開關設置 VOUT = 0.51V,針對閉合的開關設置 V OUT = 0.31V。在這些值中,會考慮 CAMM2 連接器和 PCB 上的 10mV 壓降,如 JESD318A 中為 VDDQ 通用電力輸送方法提出的建議。

電壓電平切換的定義如圖 7 所示。

圖 7 TPS628303 DVFSQ

圖 7 TPS628303 DVFSQPMIC5100 的 VIN_BULK 電源可用作一個外部基準電壓并以此作為示例,但是 TPS62830x 輸出電壓精度現在也取決于這個外部電壓。

TPS62830x–雙源封裝

TPS62830x 器件系列提供兩種封裝類型(QFN 和 SOT583),它們之間的布局兼容。在設計階段考量時,電路板設計人員可以將兩種封裝尺寸重疊,如圖 8所示。這種重疊可以讓您靈活地在封裝之間切換并緩解任何潛在的電源問題。

圖 8 重疊的 QFN 和 SOT583 封裝

圖 8 重疊的 QFN 和 SOT583 封裝