ZHCACA3A January 2022 – February 2022 LM4050QML-SP , LMP7704-SP

設計仿真

- 輸入和輸出范圍

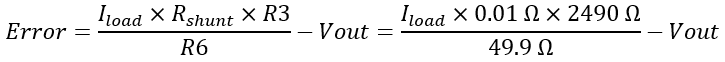

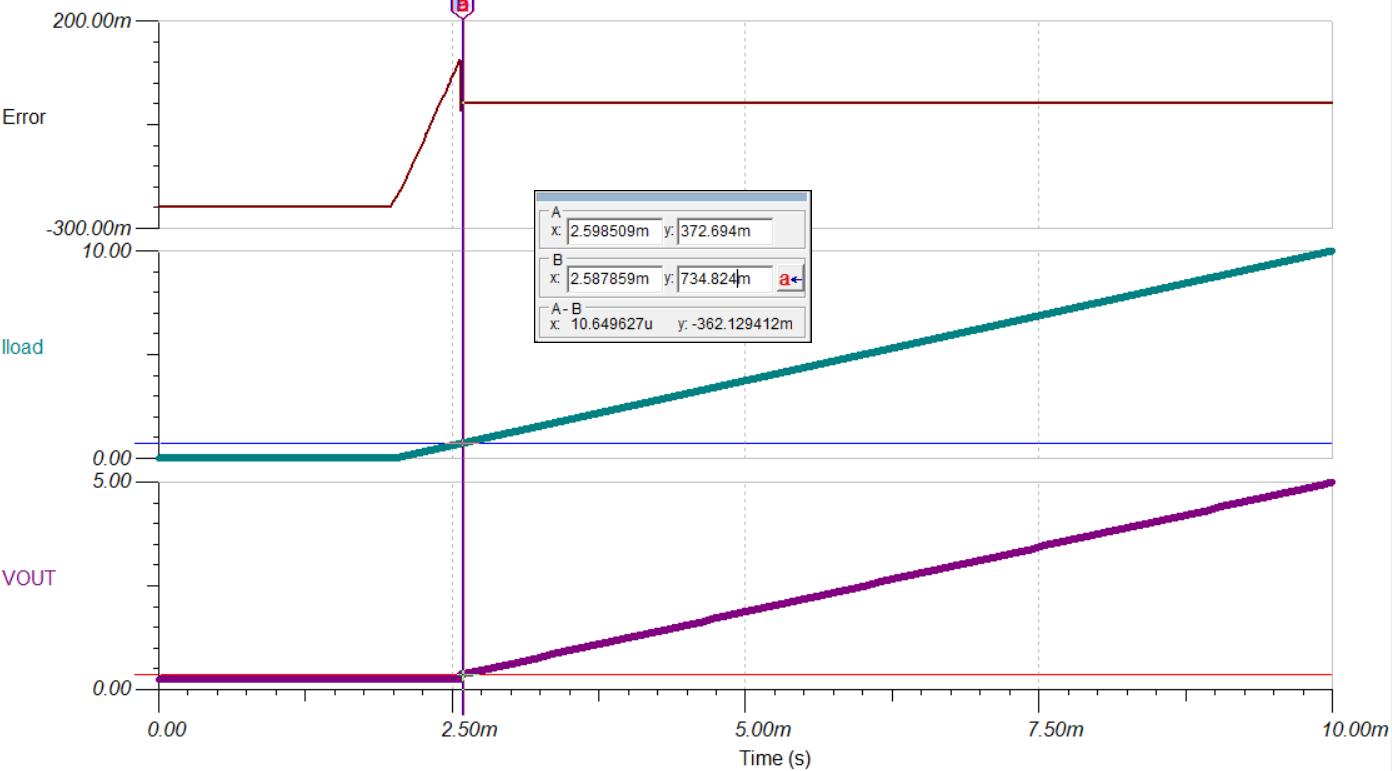

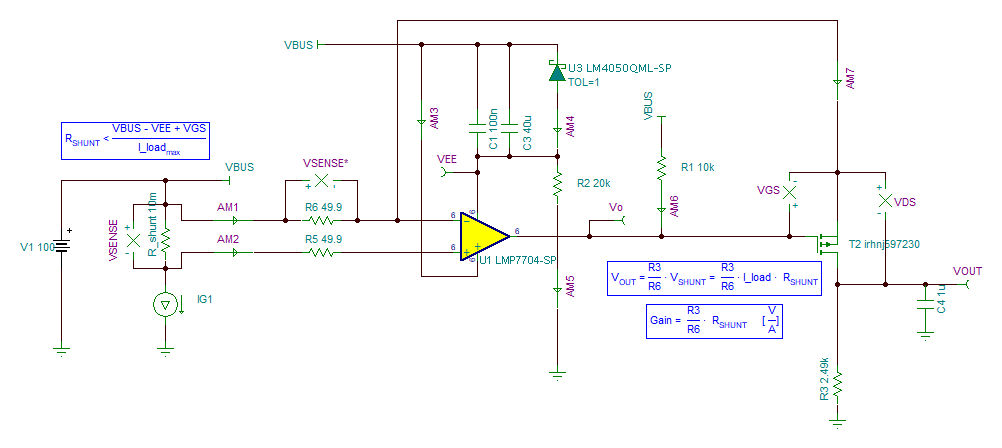

下圖顯示了 2.49kΩ (R3) 電阻器上的輸出電壓。根據以下公式計算誤差:

理想情況下,當負載電流 (Iload) 在 0A 至 10A 之間擺動時,Vout 在 0V 至 5V 之間擺動。但是,Vout 的最小值為 373mV,并且在負載電流 (Iload) 上升至 735mV 之前是非線性的。

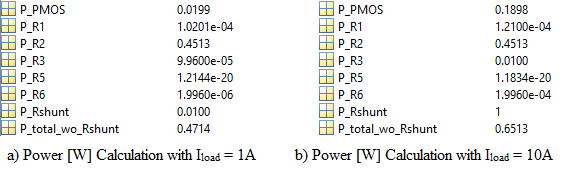

- 功耗

以下仿真和計算顯示了具有不同負載電流的電路中每個元件的功耗。在不考慮 R_shunt 功耗的情況下,總功耗為 471.4mW 至 651.3mW。R2 決定了功耗。

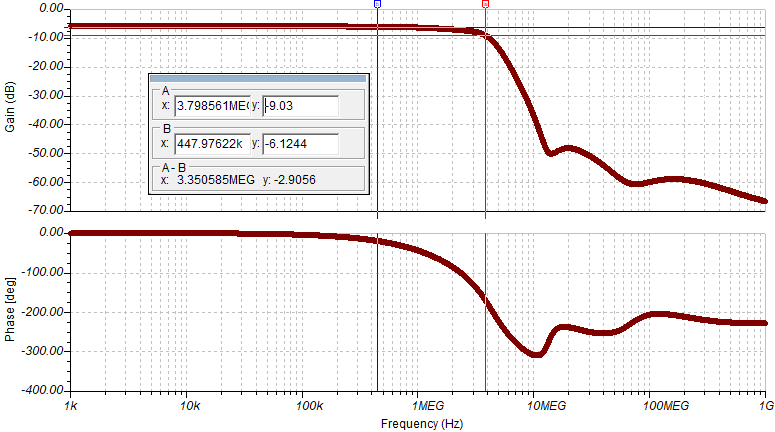

- 帶寬

下圖顯示了電路的增益,其中增益 = Vout (V) / Iload (A)。負載電容為 15pF 時,1% 的全功率帶寬和 3dB 帶寬為 478kHz 和 3.8MHz。

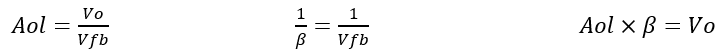

- 穩定性分析

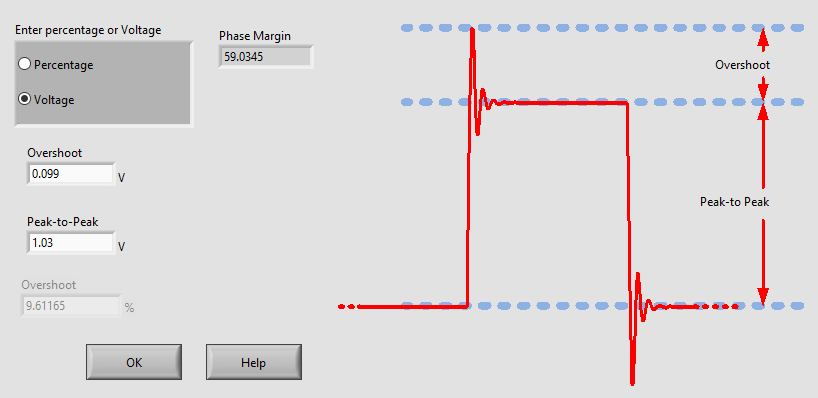

通過測量系統的相位裕度并應用小信號瞬態階躍響應來驗證系統的穩定性。為了確保穩定性,在 AOL 曲線與 1/β 交點處測量的相位裕度需要至少為 45 度。

如以下原理圖所示,在反饋回路中添加了一個 1μF 電容器以提高穩定性。以下開環交流仿真在輸入處斷環,并使用以下公式來繪制相關曲線:

上圖顯示了頻域仿真結果。相位裕度是在 1/? 和 AOL 交點處測量的,為 58.3 度,表示系統穩定。

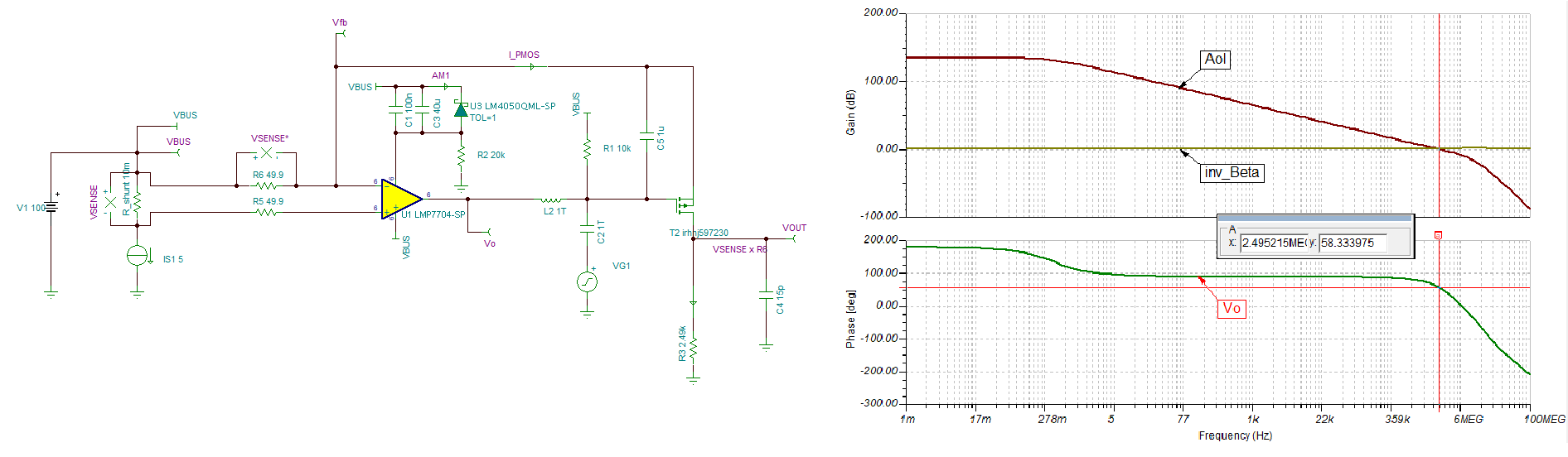

為了進一步確保穩定性,在電路的輸入端 (IG1) 上施加了小信號瞬態階躍響應,并在 Vo 上測量過沖百分比。下圖中的過沖表示相位裕度為 59 度,進一步確認了系統的穩定性。

- 故障分析警告: 如果 LMP7704-SP 運算放大器損壞且 PMOS 柵極懸空,則可能會損壞微控制器或 ADC。

有必要在 PMOS 柵極前放置一個 10kΩ 的上拉電阻 (R1),以上拉 PMOS 柵極并保護 ADC 或微控制器。

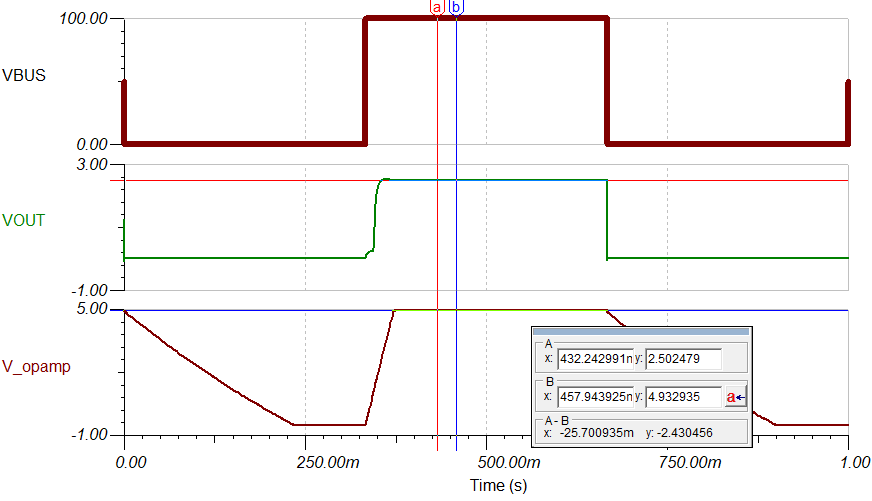

另一個故障考慮因素是運算放大器 (LMP7704-sp) 是否會被 100V Vbus 損壞。要對其進行仿真,需要在 Vbus 上施加 100V 的峰峰值方波。請參閱下圖中的仿真結果。

Vbus 和 VEE 之間的差值 V_opamp 始終低于 4.933V。LMP7704 專為高達 12V 的電源而設計,因此不會損壞。在仿真中,負載電流設置為 5A。正如預期的那樣,Vout 被仿真為大約 2.5V。

- 誤差計算

要分析電路的輸出誤差,需要使用以下參數

- Vos:運算放大器失調電壓誤差 (V)

- Vos_drift:溫漂 (V/°C)

- CMRR:共模抑制比 (dB)

- PSRR:電源抑制比 (dB)

- temp:溫度 (°C)

- Vcm_sys:共模電壓 (V),此應用中為 5V

- Vcm_ds:數據表中用于測試的共模電壓 (V)。

- R1:R6 電阻值 (Ω)

- R_shunt:分流電阻器值 (?)

- Rshunt_tol:分流電阻器容差 (%)

- TC_shunt:分流電阻器溫度系數 (ppm/°C)

- Iload:輸出電流 (A)

- Ib:輸入偏置電流 (A)

- R1_tol:R6 電阻器容差 (%)

- TC1:R6 電阻器溫度系數 (ppm/°C)

- R2_tol:R3 電阻器容差 (%)

- TC2:R3 電阻器溫度系數 (ppm/°C)

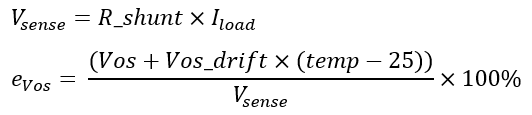

失調電壓誤差:

CMRR 誤差:

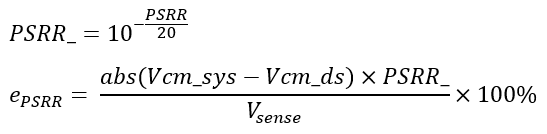

PSRR 誤差:

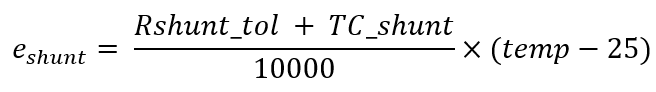

分流電阻器誤差:

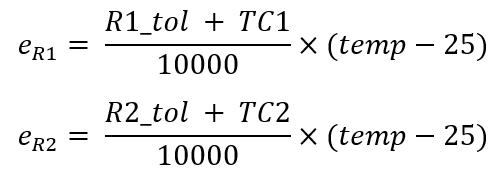

電阻器(R3 和 R6)誤差:

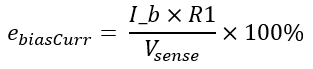

偏置電流誤差:

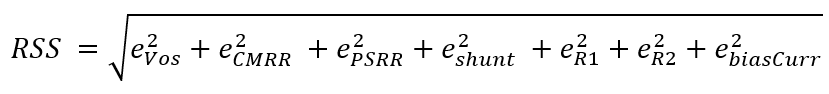

平方根 (RSS) 總誤差:

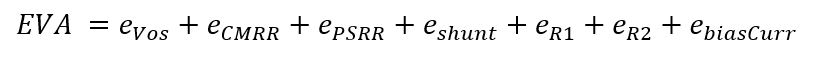

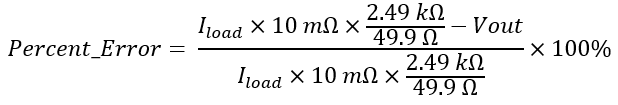

極值分析 (EVA):

在 MATLAB 中執行了之前的誤差公式,仿真結果如下圖所示。

當負載電流為 1A 時,RSS 為 0.658%。此 RSS 滿足 0.7% 的誤差要求。右側還提供了 EVA 圖作為參考。

先前的結果是在 R_shunt 設置為 10mΩ 的情況下計算得出的。當負載電流為 1A 時,運算放大器 Vos 決定了誤差。當負載電流為 10A 時,分流電阻容差決定了誤差。

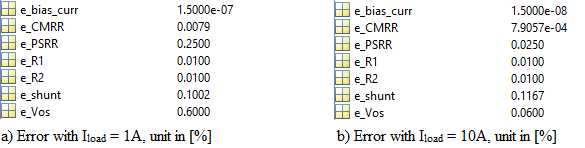

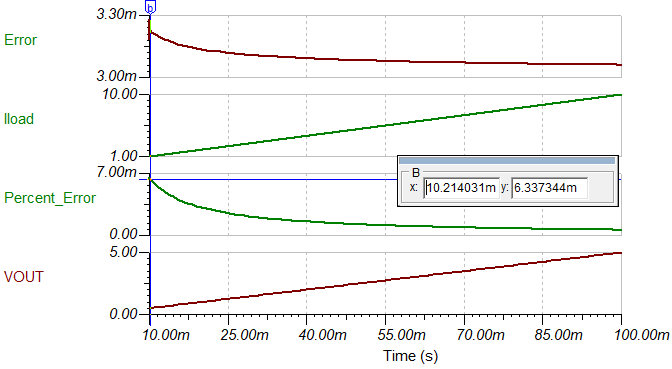

通過 TINA-TITM 仿真再次驗證先前的誤差計算,結果如下圖所示。

使用以下公式計算百分比誤差。

如仿真所示,當負載電流為 1A 時,誤差為 0.63%。該誤差與之前 MATLAB 計算中 0.6% 的 Vos 誤差一致。TINA-TITM 不對由電阻器容差和分流電阻器上溫度變化引起的誤差進行仿真。