ZHCAEC9 August 2024 SN74AC244 , SN74AC244-Q1 , SN74AC245 , SN74AC245-Q1

引言

交流邏輯系列產品提供一些在當今市場上速度超快、驅動強度超高的單端邏輯緩沖器。隨著高速和重負載的出現,溫度會大幅升高。在本文檔中,我們通過一些示例展示了如何利用提供的熱指標來確定應用特定的限制。

有許多不同的電子產品具有中高速數字信號驅動要求的特定用例。脈寬調制 (PWM) 常用于電機轉速控制、功率調節、LED 控制和音頻放大。通過使數字信號在高電平狀態 (ON) 和低電平狀態 (OFF) 之間交替,可產生 PWM 信號;通過改變脈沖寬度(高電平狀態信號的持續時間)、增加或減少占空比以及提高或降低頻率,可改變 PWM 信號。數字緩沖器可用于重新驅動 PWM 信號,以適應各種頻率和占空比的各種應用。

圖 1 機架式服務器

圖 1 機架式服務器 圖 2 印刷電路板布線

圖 2 印刷電路板布線機架式服務器通常具有控制阻抗的布線,這需要強大的驅動器。交流邏輯系列支持直接驅動 50Ω 布線,并支持相對較高的速度和重負載。一般而言,12cm 以下的布線會增加電容而不會影響傳輸線路,而 12cm 以上的布線則需要控制阻抗和正確端接以減輕對傳輸線路的影響。要將 SN74AC244 等交流驅動器用于此類應用,必須選擇與傳輸線路阻抗匹配的源端接。有關詳細信息,請參閱邏輯產品的設計注意事項。

低壓繼電器在測試和測量以及其他工業應用中很常見。交流邏輯系列的高驅動強度和集成輸出鉗位二極管允許直接驅動低壓繼電器。這些繼電器通常用于控制電流較高的負載,如伺服電機、音頻放大器和溫度傳感器。低壓繼電器可通過 5V 和最高 30mA 的電流驅動。微控制器、FPGA 和 CPU 很少具有直接驅動這些設備所需的驅動強度水平。SN74AC244 能夠以每通道 24mA 的電流驅動全部八個通道,這使得 SN74AC244 成為此應用的理想選擇,并支持在系統中使用上述繼電器。

功率計算

溫度升高是由半導體器件的功耗引起的。為了準確計算 CMOS 邏輯門的功耗,我們必須定義幾個術語和公式。

在方程式 1 中,有總功率 (PTOTAL)、靜態功率 (PS)、瞬態功率 (PT)、容性負載功率 (PLC)、負電阻負載功率 (PLRN) 和正電阻負載功率 (PLRP)。負載功率值(PLC、PLRN 和 PLRP)具體指 CMOS 邏輯器件驅動這些負載所消耗的功率。功耗公式分量 PS、PLRN 和 PLRP 可視為恒定功耗,不因工作頻率而變化,而 PT 和 PLC 分量均與頻率有關。

在方程式 2 中,有暫態功耗 (PT)、功率耗散電容 (Cpd)、電源電壓 (VCC)、輸入頻率 (fi)、通道切換次數 (NSW)。此公式假設所有通道都以相同的頻率切換,并具有相同的功率耗散電容值。

在方程式 3 中,有容性負載功率耗散 (PLC)、電源電壓 (VCC)、容性負載 (CL)、輸出頻率 (fo) 和通道切換次數 (NSW)。

在方程式 4 中,有靜態功耗 (PS)、電源電壓 (VCC) 和靜態電源電流 (ICC)。

在方程式 5 中,有負電阻負載功率耗散 (PLRN)、輸出占空比 (Do)、電源電壓 (VCC)、輸出高電平狀態電壓 (VOH) 和輸出下拉電阻 (RPD)。

在方程式 6 中,有正電阻負載功率耗散 (PLRP)、輸出占空比 (Do)、電源電壓 (VCC)、輸出高電平狀態電壓 (VOH) 和輸出上拉電阻 (RPU)。

在對 CMOS 邏輯門進行熱計算時,通常可以忽略電阻和靜態功耗值,因為這些值通常不會對總功耗產生很大的影響。為了完整起見,本文檔中包含了這些計算,但在下面的示例中,您可以了解到為何這些值對于熱耗散計算通常是不必要的。

以下各節提供了 SN74AC244 器件在常見應用中計算得出和經試驗臺驗證的熱性能。

應用 1:計算

SN74AC244 提供八個獨立的緩沖器。在此應用中,我們將全部八個輸入連接到單個 10MHz、50% 占空比時鐘源,并使用每個輸出驅動獨立負載。使用共享時鐘輸入分成多路輸出稱為時鐘扇出應用。

輸出負載相當于大約 10 個 CMOS 器件輸入,每個通道的總容性負載 (CL) 為 56pF,每個通道的總電阻負載為 500kΩ(RLP 和 RLN)。CL 是測試時本地可用的接近 50pF 的值。RLP 和 RLN 值是根據電源電壓 5V 和假設每個輸入的最大輸入漏電流為 1μA 計算得出的。當有 10 個并聯輸入時,在 5V 下最大為 10μA,相當于 500kΩ。

首先,我們計算靜態功耗值。在將值代入到給定的公式中之前,我們需要確定此負載條件下的 VOH 和 VOL 值。數據表提供了最壞情況下 4.5V 電源 VOH 在 50μA 負載下為 VCC - 0.1V,VOL 在相同負載下為 0.1V。我們的負載是原來的十分之一,因此電壓也是原來的十分之一,結果為 VCC - VOH = 0.01V,VOL = 0.01V。

在本應用中,所有靜態源的總功耗小于 1mW。四舍五入為 1mW,并選擇功耗最高的封裝 PW (TSSOP),我們可以根據此功耗 (1mW) 和數據表中給出的 RθJA 126.2°C/W 計算出溫升。由 1mW 的功耗和相關的熱阻值得出的溫升小于 0.13°C,換句話說,可以忽略不計。需要明確的是,由于這些功耗值的影響很小,上述計算對于正常應用而言并非必要,但為了完整性起見,并說明在 CMOS 邏輯器件的大多數應用中可以忽略靜態功耗的原因,此處包括了這些計算。

接下來看看動態功率耗散,它的功耗更大。Cpd 值取自數據表,為 45pF。

這兩個值相加得到 202mW,這是相當大的功耗。根據這些數字得出,器件采用 PW 封裝時的溫升約為 25.5°C (0.202W × 126.2°C/W = 25.49°C)。

假設結溫最高為 150°C,器件的環境工作溫度最高為 125°C,則 SN74AC244 幾乎可以在整個環境工作溫度范圍內以這種功率級別運行。在高端,器件限制為 124.5°C,以避免超過最高結溫 150°C。

針對 DGS 封裝 (RθJA = 123.5°C/W) 重復上述計算,得到溫度升高 24.9°C,導致 TJ(max) 為 149.9°C。溫度升高表明 DGS 封裝的熱性能略有改善,并且此應用能夠在整個溫度范圍內使用該器件。

應用 1:基準測試

在我們的實驗中,我們只能測量器件的外殼溫度,因此必須根據實驗數據計算結溫。用于本實驗的 PCB 來自 14-24-LOGIC-EVM。這些電路板未根據應用報告半導體和 IC 封裝熱指標 針對熱導率進行優化,但確實代表了典型的雙層電路板設計。

根據應用報告半導體和 IC 封裝熱指標,“RθJA 不但是封裝的變量函數,而且是許多其他系統級特性(例如已安裝該器件的印刷電路板 (PCB) 的設計和布局)的變量函數。實際上,測試板是一個焊接在器件引線上的散熱器。更改測試板的設計或配置也會改變散熱器的效率,并因此改變測得的 RθJA。”

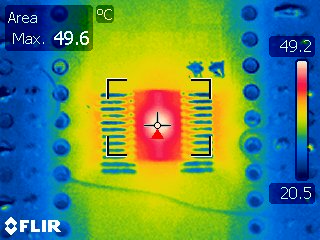

圖 3 PW 封裝在 10MHz、5V 電源、8 個通道切換(每個通道 56pF 負載)下運行的熱感圖像

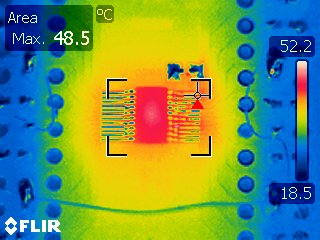

圖 3 PW 封裝在 10MHz、5V 電源、8 個通道切換(每個通道 56pF 負載)下運行的熱感圖像 圖 4 DGS 封裝在 10MHz、5V 電源、8 個通道切換(每個通道 56pF 負載)下運行的熱感圖像

圖 4 DGS 封裝在 10MHz、5V 電源、8 個通道切換(每個通道 56pF 負載)下運行的熱感圖像工作結溫可以使用方程式 14 通過測得的外殼溫度計算得出。每個封裝的溫度均在先前計算的條件下測量(TA = 25°C、VCC = 5V、fin = 10MHz、CL = 56pF、RP = RL = 500kΩ),值在表 1中提供。每種情況下計算得出的總功耗為 202mW。

| 測量的外殼溫度 (°C) | ΨJT (°C/W) | 計算得出的結溫 | 計算得出的溫升 | 數據表指定的 RθJA | 計算得出的應用特定 RθJA | |

| PW | 49.6 | 22.3 | 53.8 | 28.8 | 126.2 | 151.8 |

| DGS | 48.5 | 7.8 | 50.0 | 25 | 123.5 | 131.5 |

數據表提供的 RθJA 與根據本實驗計算出的 PW 封裝的應用特定 RθJA 之間存在很大差異。數據表計算的熱阻值與實驗得出的熱阻值之差在應用報告半導體和 IC 封裝熱指標 中進行了詳細說明,不過我們可以在此簡要重申,PCB 設計對器件的熱性能有很大影響,并且此 PCB 并未針對熱性能進行優化。

本實驗的核心結論是,DGS 封裝可顯著節省空間,同時還可提高導熱性。此外,根據數據表熱規格計算出的 25.5°C 溫升接近實驗得出的 28.8°C 和 25°C 值,這證實了計算值是構建電路板之前估算熱性能的有效方法,即使對于非理想的 PCB 設計也是如此。

應用 2:計算

在此應用中,我們再次使用 SN74AC244 并使用與應用 1:計算中所述的相同條件。與應用 1 的區別在于封裝和 PCB。在此應用中,我們使用 RKS (WQFN) 封裝,并根據數據表中的建議,測試一塊散熱焊盤懸空的 PCB 和另一塊散熱焊盤連接到接地平面的 PCB。

有關詳細信息,請參閱應用 1:計算,因為該應用的負載和功率耗散計算是相同的。

此應用之前計算的功耗為 202mW。在 RKS 封裝中 (RθJA = 67.7°C/W),SN74AC244 預期溫升約為 13.7°C (0.202W× 67.7°C/W = 13.67°C),因此在 TA = 25°C 時結溫為 38.7°C。

假設結溫最高為 150°C,器件的最高環境工作溫度為 125°C,根據計算得出的溫升,SN74AC244 能夠在整個環境工作溫度范圍內以該功率級別持續運行。

應用 2:基準測試

在我們的實驗中,我們只能測量器件的外殼溫度,因此必須根據實驗數據計算結溫。本實驗使用的一塊 PCB 來自 14-24-LOGIC-EVM,而另一塊是經過修改的版本,其中含有將散熱墊連接到地的通孔,同時保持所有其他電路板功能、層疊和幾何形狀。這些電路板未根據應用報告半導體和 IC 封裝熱指標 針對熱導率進行優化,但確實代表了典型的雙層電路板設計。

根據應用報告半導體和 IC 封裝熱指標,“RθJA 不但是封裝的變量函數,而且是許多其他系統級特性(例如已安裝該器件的印刷電路板 (PCB) 的設計和布局)的變量函數。實際上,測試板是一個焊接在器件引線上的散熱器。更改測試板的設計或配置也會改變散熱器的效率,并因此改變測得的 RθJA。”

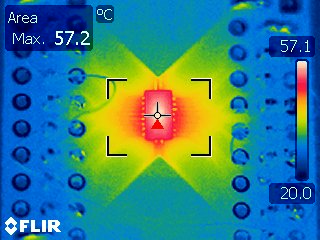

圖 5 RKS 封裝在 10MHz、5V 電源、8 個通道切換(每個通道 56pF 負載,散熱焊盤連接懸空)下運行的熱感圖像

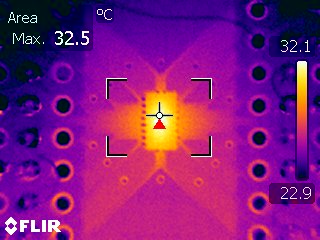

圖 5 RKS 封裝在 10MHz、5V 電源、8 個通道切換(每個通道 56pF 負載,散熱焊盤連接懸空)下運行的熱感圖像 圖 6 RKS 封裝在 10MHz、5V 電源、8 個通道(每個通道 56pF 負載,散熱焊盤連接到接地平面)下運行的熱感圖像

圖 6 RKS 封裝在 10MHz、5V 電源、8 個通道(每個通道 56pF 負載,散熱焊盤連接到接地平面)下運行的熱感圖像工作結溫可以使用方程式 14 通過測得的外殼溫度計算得出。每個封裝的溫度均在先前計算的條件下測量(TA = 25°C、VCC = 5V、fin = 10MHz、CL = 56pF、RP = RL = 500kΩ),值在表 1中提供。每種情況下計算得出的總功耗為 202mW。

| 測量的外殼溫度 (°C) | ΨJT (°C/W) | 計算得出的結溫 (°C) | 計算得出的 (1) 溫升 (°C) | 數據表指定的 RθJA (°C/W) | 計算得出的(2)應用特定 RθJA (°C/W) | |

| 帶懸空散熱焊盤的 RKS | 57.2 | 10.3 | 59.3 | 34.3 | 67.7 | 169.7 |

| 帶接地散熱焊盤的 RKS | 32.5 | 10.3 | 34.6 | 9.6 | 67.7 | 47.4 |

如前一應用中所述,PCB 設計對器件的熱性能具有巨大影響。所提供的數據表明,通過按照數據表建議將導熱焊盤連接到底層接地平面,RKS 封裝的熱性能得到顯著改善。憑借良好的散熱設計,RKS 封裝具有出色的散熱特性,并且比其他封裝選項更節省空間。