ZHCAEC8 August 2024 TAC5111-Q1 , TAC5212-Q1 , TAC5311-Q1 , TAC5312-Q1 , TAC5411-Q1 , TAC5412-Q1 , TAD5212-Q1

3.2 限制器響應

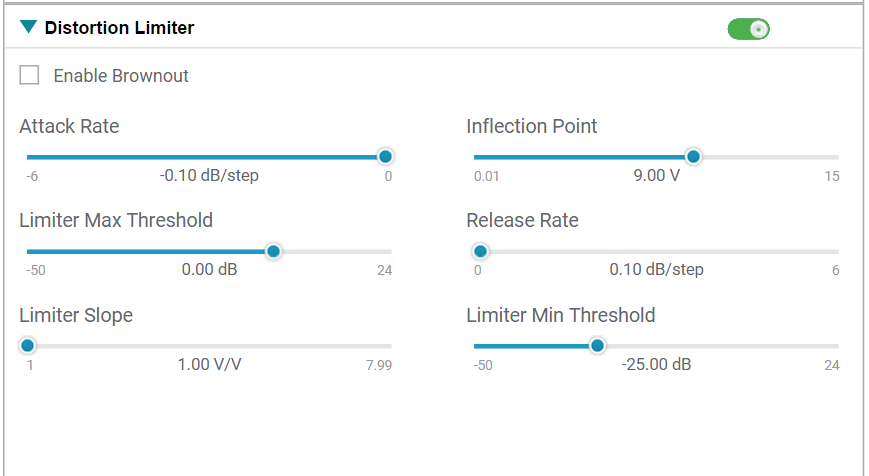

失真限制器 驗證的設置(如圖 3-3 所示)可以通過直接的 I2C 通信進行編程,并可以在 PurePath? Console 3 軟件中進行配置。

圖 3-3 失真限制器 PPC3 配置

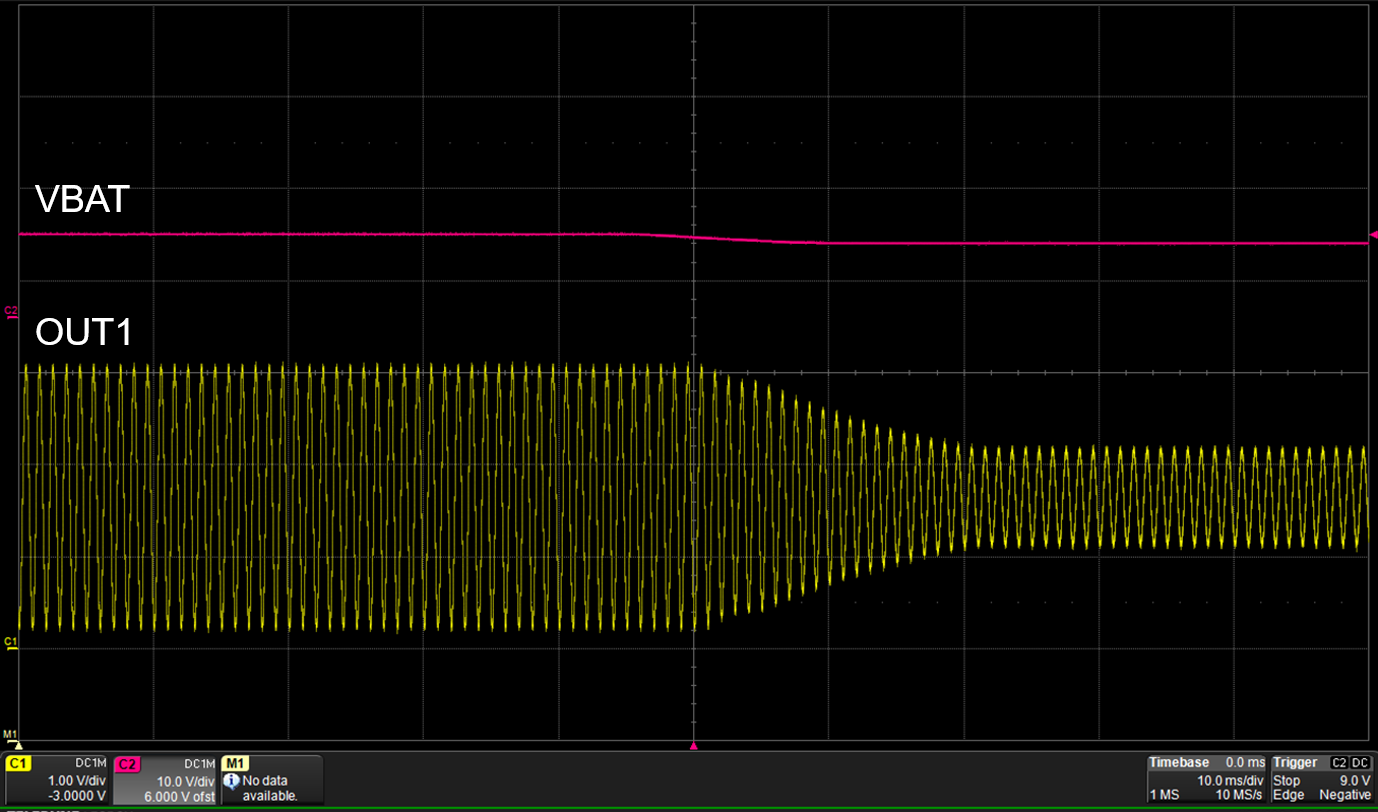

圖 3-3 失真限制器 PPC3 配置圖 3-4 的示波器截圖顯示了限制器主動調整增益的示例。在該示例中,由臺式電源提供并在通道 2 上表示的 VBAT 隨著時間的推移而斜降,從而使限制器生效。在拐點之前,通道 1 上的輸出信號為滿量程 2Vrms 信號,隨著 VBAT 下降而衰減到大約 120mVrms。

圖 3-4 失真限制器啟動曲線

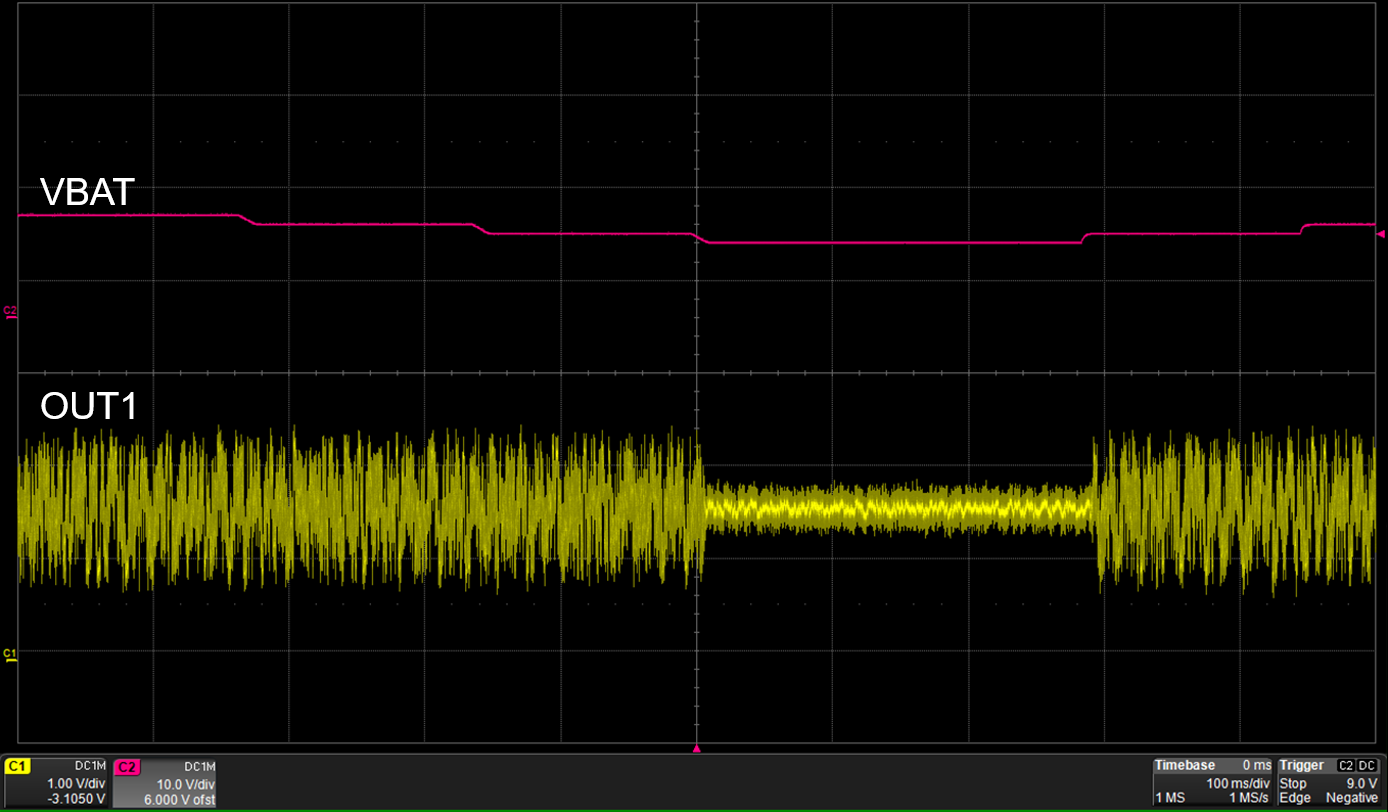

圖 3-4 失真限制器啟動曲線圖 3-5 所示為隨著 VBAT 下降并突然回升至高于拐點的水平而產生的限制器啟動和釋放速率的一個示例。

圖 3-5 失真限制器兩級響應

圖 3-5 失真限制器兩級響應