ZHCSXQ0I July 1997 – January 2025 SN54AHC123A , SN74AHC123A

PRODUCTION DATA

- 1

- 1 特性

- 2 說(shuō)明

- 3 引腳配置和功能

- 4 規(guī)格

- 5 參數(shù)測(cè)量信息

- 6 詳細(xì)說(shuō)明

- 7 應(yīng)用和實(shí)施

- 8 器件和文檔支持

- 9 修訂歷史記錄

- 10機(jī)械、封裝和可訂購(gòu)信息

封裝選項(xiàng)

請(qǐng)參考 PDF 數(shù)據(jù)表獲取器件具體的封裝圖。

機(jī)械數(shù)據(jù) (封裝 | 引腳)

- DB|16

- PW|16

- N|16

- D|16

- DGV|16

散熱焊盤(pán)機(jī)械數(shù)據(jù) (封裝 | 引腳)

訂購(gòu)信息

3 引腳配置和功能

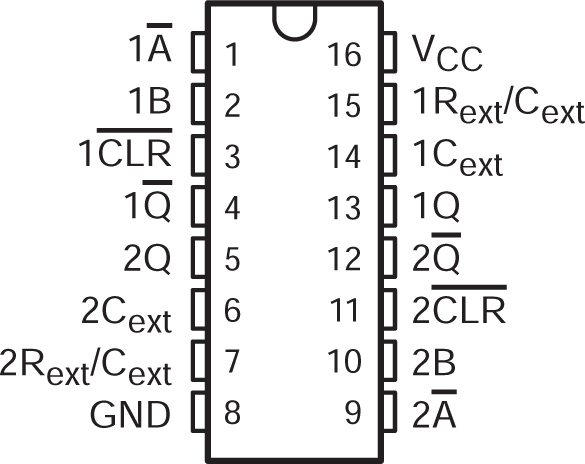

圖 3-1 SN54AHC123A J 或 W 封裝;SN74AHC123A D、DB、DGV、N、或 PW Package封裝;16-引腳 CDIP、CFP、SOIC、SSOP、TVSOP、PDIP、TSSOP (頂視圖)

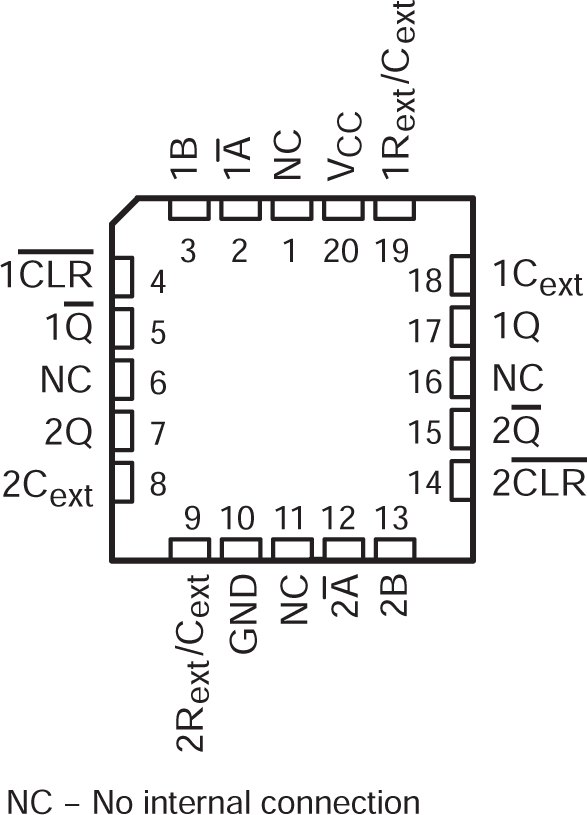

圖 3-1 SN54AHC123A J 或 W 封裝;SN74AHC123A D、DB、DGV、N、或 PW Package封裝;16-引腳 CDIP、CFP、SOIC、SSOP、TVSOP、PDIP、TSSOP (頂視圖) 圖 3-2 SN54AHC123A FK 封裝,20 引腳 LCCC(頂視圖)

圖 3-2 SN54AHC123A FK 封裝,20 引腳 LCCC(頂視圖)表 3-1 引腳功能

| 引腳 | I/O1 | 說(shuō)明 | |

|---|---|---|---|

| 名稱 | 編號(hào) | ||

| 1 A | 1 | I | 當(dāng) 1B = H 時(shí)通道 1 下降沿觸發(fā)輸入;采用其他輸入方法時(shí)保持低電平 |

| 1B | 2 | I | 在 1 A = L 時(shí),通道 1 上升沿觸發(fā)輸入;采用其他輸入方法時(shí)保持高電平 |

| 1 CLR | 3 | I | 在 1 A = L 和 1B = H 時(shí),通道 1 上升沿觸發(fā);采用其他輸入方法時(shí)保持高電平;可以通過(guò)在輸出期間驅(qū)動(dòng)低電平來(lái)縮短脈沖長(zhǎng)度 |

| 1 Q | 4 | O | 通道 1 反相輸出 |

| 2Q | 5 | O | 通道 2 輸出 |

| 2Cext | 6 | — | 通道 2 外部電容器負(fù)極連接 |

| 2Rext/Cext | 7 | — | 通道 2 外部電容器和電阻器結(jié)連接 |

| GND | 8 | — | 接地 |

| 2 A | 9 | I | 當(dāng) 2B = H 時(shí)通道 2 下降沿觸發(fā)輸入;采用其他輸入方法時(shí)保持低電平 |

| 2B | 10 | I | 在 2 A = L 時(shí),通道 2 上升沿觸發(fā)輸入;采用其他輸入方法時(shí)保持高電平 |

| 2 CLR | 11 | I | 在 2 A = L 和 2B = H 時(shí),通道 2 上升沿觸發(fā);采用其他輸入方法時(shí)保持高電平;可以通過(guò)在輸出期間驅(qū)動(dòng)低電平來(lái)縮短脈沖長(zhǎng)度 |

| 2 Q | 12 | O | 通道 2 反相輸出 |

| 1Q | 13 | O | 通道 1 輸出 |

| 1Cext | 14 | — | 通道 1 外部電容器負(fù)極連接 |

| 1Rext/Cext | 15 | — | 通道 1 外部電容器和電阻器結(jié)連接 |

| VCC | 16 | — | 電源 |

- I = 輸入,O = 輸出,I/O = 輸入或輸出,G = 地,P = 電源