ZHCABN2 February 2022 UCC14240-Q1

11 使能 (ENA) 和電源正常引腳 (/PG)

UCC14240-Q1 包含初級參考的、 5V TTL 和 3.3V LVTTL 邏輯兼容的、高電平有效使能功能。強制 ENA 為低電平會禁用器件,并將其置于非開關待機模式,此時電流消耗降至 500μA 以下。將 ENA 引腳拉至高電平(高于 2V 閾值)會激活正常的器件功能。ENA 引腳有一個較弱的內部下拉電阻,因此如果該引腳處于開路狀態,ENA 引腳將懸空到禁用狀態。如果不使用 ENA,則應將其拉高至 2.5V<VENA<5.5V 之間的電壓。應注意確保 VENA 不超過 5.5VMAX。

低電平有效、電源正常 (/PG) 引腳為開漏輸出,用于指示 UCC14240-Q1 何時不存在故障且輸出電壓在其調節設定點的 ±10% 范圍內。將 /PG 引腳上的上拉電阻 (>1kΩ) 連接到 5V 或 3.3V 邏輯軌。對于不使用 /PG 信號的應用, /PG 可以直接連接到 GNDP。

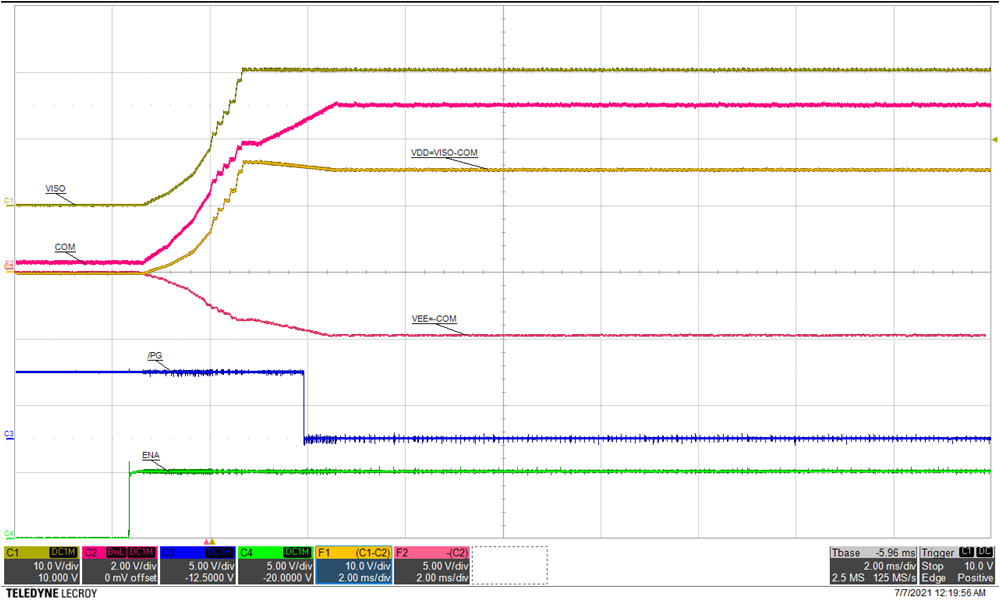

圖 11-1 中的啟動波形顯示了 /PG 相對于 ENA 的預期行為。輸入電壓(VIN=24V,未顯示)已經存在,UCC14240-Q1 由 ENA 變為高電平而激活。ENA 高電平和 /PG 低電平之間的測量時間約為 3.75ms,但可以根據隔離輸出電壓在設定調節值的 ±10% 范圍內所需的時間而變化。相對于 VDD-VEE,COM-VEE 達到調節所需的時間較長,這會導致 VDD-COM 出現輕微的過沖,但這是在 /PG 達到其低電平有效狀態之前發生的。這突顯了在 /PG 進入有效低電平狀態之前請勿切換柵極驅動器的重要性。請注意,此處介紹的波形是從 UCC14240EVM-052 EVM 捕獲的。使用 UCC14240EVM-052 用于偏置需要單、正或雙、正/負偏置電源的牽引逆變器柵極驅動器 IC 是 EVM 用戶指南,其中包含原理圖、PCB 詳細信息和測量到的性能數據。

圖 11-1 啟動:VIN=24V,IDD=80mA(頂部:VISO (VDD-VEE),10V/div,中間 1:COM,2V/div,中間 2:VDD=VISO-COM,10V/div,中間 3:VEE=-COM,5V/div,中間 4:/PG,5V/div,底部:ENA,5V/div),時間 = 2ms/div(除非另有說明)。

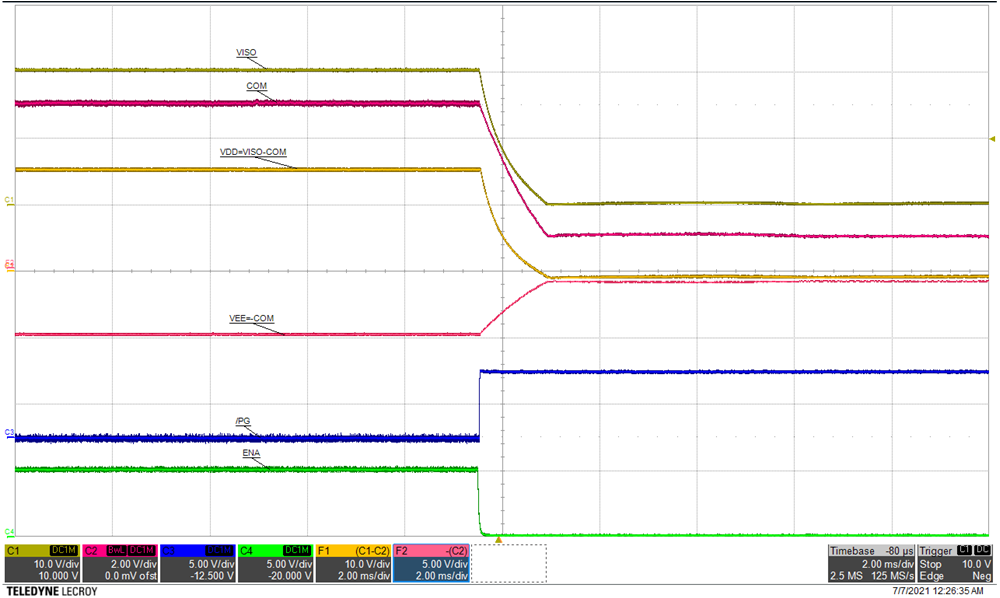

相反,圖 11-2 中的關斷波形顯示,只要 ENA 被拉至為低電平,UCC14240-Q1 輸出電壓就會以受控方式放電,并且 /PG 在相對于 ENA 幾乎沒有延遲的情況下切換為高電平。

圖 11-2 關斷:VIN=24V,IVDD=80mA(頂部:VISO (VDD-VEE),10V/div,中間 1:COM,2V/div,中間 2:VDD=VISO-COM,10V/div,中間 3:VEE=-COM,5V/div,中間 4:/PG,5V/div,底部:ENA,5V/div),時間 = 2ms/div(除非另有說明)。